Horizon 2020 European Union funding for Research & Innovation

5G Programmable Infrastructure Converging disaggregated network and compUte Resources

## D3.2 Intermediate report on Data Plane Programmability and infrastructure components

This project has received funding from the European Union's Framework

Programme Horizon 2020 for research, technological development and

### demonstration

5G PPP Research and Validation of critical technologies and systems

Project Start Date: June 1st, 2017

Call: H2020-ICT-2016-2

Topic: ICT-07-2017

Duration: 33 months

Date of delivery: 30th November 2018

Version 1.0

Project co-funded by the European Commission Under the H2020 programme

Dissemination Level: Public

| Grant Agreement Number: | 762057                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project Name:           | 5G Programmable Infrastructure Converging dis-<br>aggregated network and compUte REsources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Project Acronym:        | 5G-PICTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Document Number:        | D3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Document Title:         | Intermediate report on Data Plane Programmability and infrastructure components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Version:                | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Delivery Date:          | 30 <sup>th</sup> November 2018                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Responsible:            | Consorzio Nazionale Interuniversitario per le<br>Telecomunicazioni (CNIT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Editor(s):              | Salvatore Pontarelli (CNIT),<br>Stefan Zimmermann(ADVA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Authors:                | Jens Bartelt (AIR), August Betzler (i2CAT), Giuseppe<br>Bianchi (CNIT), Steinar Bjørnstad (TP), Marco Bonola<br>(CNIT), Daniel Camps (i2CAT), Chia-Yu Chang<br>(EUR), Jay-Kant Chaudhary (TUD), Nebojsa Maletic<br>(IHP), Marcus Ehrig (IHP), Jesús Gutiérrez (IHP),<br>Paris Flegkas (UTH), Nikos Makris (UTH), Eduard<br>García-Villegas (i2CAT/UPC), Arash Beldachi (UNI-<br>VBRIS-HPN), Joan J. Aleixendri (i2CAT), Matty Ka-<br>dosh (MLNX), Vaia Kalokidou (UNIVBRIS-CSN), Pe-<br>ter Legg (BWT), Salvatore Pontarelli (CNIT), Marco<br>Spaziani (CNIT), Anna Tzanakaki (UNIVBRIS-HPN),<br>Raimena Veisllari (TP), Stefan Zimmermann(ADVA). |

| Keywords:               | Dataplane programmability, programmable network platform, optical technologies, wireless technologies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Status:                 | Draft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Dissemination Level     | Public                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Project URL:            | http://www.5g-picture-project.eu/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **Revision History**

| Rev. N | Description                                                                                                                      | Author                                                                                                                                               | Date       |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| 0.1    | Initial Draft, initial contributions to Section 2.4                                                                              | Salvatore Pontarelli (CNIT), Marco<br>Bonola (CNIT), Giuseppe Bianchi<br>(CNIT)                                                                      | 27/06/2018 |  |  |  |

| 0.1    | Contribution of the Flex-E description and<br>the X-Ethernet description (Sections 4.3<br>and 4.4)                               | Kostas Katsalis ( <b>HWDU</b> )                                                                                                                      | 11/09/2018 |  |  |  |

| 0.1    | Contribution on the RF processing/model-<br>ling for simulation<br>(Section 4.5)                                                 | Vaia Kalokidou<br>(UNIVBRIS-CSN)                                                                                                                     | 13/09/2018 |  |  |  |

| 0.1    | Contribution on BB Processing in Active<br>Antenna Distributed Unit<br>(Section 4.6)                                             | Jens Bartelt (AIR)                                                                                                                                   | 17/09/2018 |  |  |  |

| 0.1    | Contribution to Time Sensitive Ethernet<br>(Section 2.7)                                                                         | Steinar Bjørnstad (TP)                                                                                                                               | 18/09/2018 |  |  |  |

| 0.1    | Contribution to Section 3.1                                                                                                      | Peter Legg (BWT)                                                                                                                                     | 26/09/2018 |  |  |  |

| 0.1    | Contribution on the FlexRAN platform (Section 2.5)                                                                               | Chia-Yu Chang (EUR)                                                                                                                                  | 27/09/2018 |  |  |  |

| 0.1    | Contribution on APIs for the GateWorks<br>Ventana platform (Section 3.2)                                                         | Daniel Camps, Eduard García,<br>Joan J. Aleixendri, August Betzler<br>( <mark>i2CAT/UPC</mark> )                                                     | 29/09/2018 |  |  |  |

| 0.1    | Contribution on Section 4.2                                                                                                      | Steinar Bjørnstad ( <b>TP</b> ),<br>Jim Zou ( <b>ADVA</b> )                                                                                          | 01/10/2018 |  |  |  |

| 0.1    | Contribution on OAI Interfaces for Physical<br>Network Functions (Section 3.3)                                                   | Nikos Makris (UTH),<br>Paris Flegkas (UTH)                                                                                                           | 03/10/2018 |  |  |  |

| 0.2    | First merge                                                                                                                      | Salvatore Pontarelli (CNIT)                                                                                                                          | 03/10/2018 |  |  |  |

| 0.2    | Contribution on the development of P4 compiler for Spectrum device (Section 3.4)                                                 | Matty Kadosh (MLNX)                                                                                                                                  | 08/10/2018 |  |  |  |

| 0.2    | Contribution on TSON, Sections 2.1, 2.2.<br>and 2.3                                                                              | Arash Beldachi (UNIVBRIS-HPN),<br>Anna Tzanakaki (UNIVBRIS-HPN)                                                                                      | 12/10/2018 |  |  |  |

| 0.2    | Contributions on P2MP MAC processor<br>and on LoS MIMO (Sections 2.6 and 4.7)                                                    | Marcus Ehrig ( <b>IHP</b> ),<br>Nebojsa Maletic ( <b>IHP</b> ),                                                                                      | 23/10/2018 |  |  |  |

| 0.2    | NETCONF/YANG service development<br>framework for ADVA's programmable edge<br>device platforms (Section 2.8), and Section<br>4.1 | Stefan Zimmermann (ADVA),<br>Jim Zou (ADVA)                                                                                                          | 23/10/2018 |  |  |  |

| 0.3    | Second merge<br>(at Technical Meeting in Oslo)                                                                                   | Stefan Zimmermann (ADVA)                                                                                                                             | 23/10/2018 |  |  |  |

| 0.4    | Revised version with improved formatting,<br>numbering, and additional contributions<br>from i2CAT and IHP                       | Eduard García ( <mark>i2CAT/UPC</mark> ),<br>Nebojsa Maletic ( <b>IHP</b> ),<br>Jesús Gutiérrez ( <b>IHP</b> ),<br>Stefan Zimmermann ( <b>ADVA</b> ) | 30/10/2018 |  |  |  |

| 0.5    | Further revised version with merged and<br>updated bibliography, and additional contri-<br>butions from ADVA (Section 4.8)       |                                                                                                                                                      |            |  |  |  |

| 0.6 | Revised contribution on TSON,<br>Sections 2.1, 2.2. and 2.3                                               | Arash Beldachi (UNIVBRIS-HPN)                       | 09/11/2018 |

|-----|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|

| 0.7 | Internal Review phase                                                                                     | Jens Bartelt (AIR)                                  | 10/11/2018 |

| 0.8 | Revised version after internal review phase                                                               | Salvatore Pontarelli (CNIT)                         | 12/11/2018 |

| 0.8 | Further revised version after internal re-<br>view phase, including additional correc-<br>tions from ADVA | Stefan Zimmermann (ADVA)                            | 26/11/2018 |

| 0.9 | Final revised document                                                                                    | Anna Tzanakaki (UNIVBRIS),<br>Jesús Gutiérrez (IHP) | 28/11/2018 |

| 1.0 | Submission to the EC                                                                                      | Jesús Gutiérrez (IHP)                               | 30/11/2018 |

# **Table of Contents**

| LIST OF    | FIGURES                                                                               | 8  |

|------------|---------------------------------------------------------------------------------------|----|

| LIST OF    | TABLES                                                                                |    |

| EXECUT     | TIVE SUMMARY                                                                          |    |

| 1 INT      | RODUCTION                                                                             |    |

| Organisati | ion of the document                                                                   | 13 |

|            | ICTIONAL DEFINITION OF PROGRAMMABLE PLATFORMS: IMPLE<br>'S AND PRELIMINARY EVALUATION |    |

| 2.1 Tin    | ne-Shared Optical Network (TSON) Platform                                             | 14 |

| 2.1.1      | Generic TSON functionality/architecture, capabilities, and evaluation results         |    |

| 2.1.2      | Generic TSON functionality/architecture                                               |    |

| 2.1.3      | TSON resource allocation capabilities                                                 |    |

| 2.1.4      | Generic TSON Evaluation                                                               | 16 |

| 2.2 TS     | ON extensions provided in support of FH and BH services                               | 17 |

| 2.2.1      | TSON Synchronisation                                                                  |    |

| 2.2.2      | Backhaul Services over TSON – Supporting Ethernet                                     |    |

| 2.2.3      | FH Services over TSON – CPRI extension                                                |    |

| 2.2.4      | TSON evaluation results                                                               | 21 |

| 2.3 BV     | T and TSON extensions for 5G-PICTURE                                                  | 23 |

| 2.3.1      | Real-Time Modulation-Adaptable Transmitter for 5G-PICTURE                             |    |

| 2.3.2      | TSON extensions for 5G-PICTURE                                                        | 24 |

| 2.4 Op     | en Packet Processor (OPP)                                                             | 24 |

| 2.4.1      | Hardware Implementation                                                               |    |

| 2.4.2      | Evaluation Methodology                                                                |    |

| 2.4.3      | Throughput: end-to-end tests                                                          |    |

| 2.4.4      | Latency                                                                               | 27 |

| 2.4.5      | Packet Manipulator Processor                                                          |    |

| 2.4.5      | 1                                                                                     |    |

| 2.4.5      | .2 Performance Evaluation                                                             |    |

| 2.5 Fle    | xRAN+ platform                                                                        | 29 |

| 2.5.1      | FlexRAN review                                                                        |    |

| 2.5.2      | FlexRAN+ enhancement                                                                  |    |

| 2.5.3      | FlexRAN+ evaluation                                                                   |    |

| 2.6 PT     | MP MAC processor                                                                      |    |

| 2.6.1      | Point-to-Multi-Point TDMA Medium Access Scheme                                        |    |

| 2.6.2      | Link establishment                                                                    |    |

| 2.7 NE     | TCONF server and Yang models for Time Sensitive Networks (TSN)                        | 37 |

| 2.7.1            | YANG model                                                             |        |

|------------------|------------------------------------------------------------------------|--------|

| 2.7.2            | NETCONF server                                                         |        |

| 2.7.3            | Joint NETCONF/YANG service for FUSION and passive WDM                  |        |

| 2.8 NE           | TCONF/YANG service development framework for ADVA's hardware platforms | 38     |

| 3 HAR            | RDWARE ABSTRACTIONS: PERFORMANCE ASSESSMENT AND FUNC                   | ΓΙΟΝΑΙ |

|                  | ATION                                                                  |        |

| 3.1 AP           | Is for the Typhoon platform                                            | 41     |

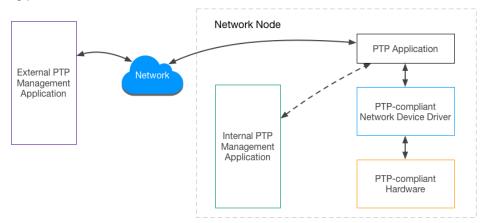

| 3.1.1            | Control and Programmability of Synchronisation Functions               |        |

| 3.1.2            | The IEEE 1588 Management Interface                                     |        |

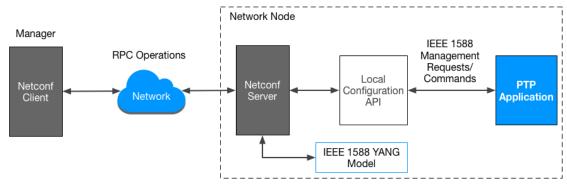

| 3.1.2.           | 1 NETCONF                                                              | 45     |

| 3.1.2.           | 2 OpenFlow and Open vSwitch                                            |        |

| 3.2 AP           | Is for the GateWorks Ventana platform                                  |        |

| 3.2.1            | YANG and NETCONF                                                       |        |

| 3.2.2            | Northbound REST API                                                    |        |

| 3.2.3            | Functional evaluation and performance                                  |        |

| 3.3 OA           | I Interfaces for Physical Network Functions                            | 51     |

| 3.4 Pro          | ogramming languages for data plane programmability                     | 52     |

| 3.4.1            | P4 compiler                                                            |        |

| 3.4.1.           | 1 Development of P4 compiler for Spectrum device                       | 53     |

| 3.4.1.           | 2 Mellanox P4 Compiler main components                                 | 53     |

| 3.4.1.           | 3 Mellanox P4 Compiler                                                 | 55     |

| 3.4.1.           | 4 Mellanox P4 API                                                      | 56     |

| 3.4.2            | ADVA P4 Xilinx FGPA development workflow                               | 56     |

| 3.4.3            | XTRA language                                                          | 58     |

| 3.5 NE           | TCONF/YANG service for ADVA's passive WDM platform                     | 62     |

|                  |                                                                        |        |

|                  | RDWARE TECHNOLOGIES: IMPLEMENTATION RESULTS AND PERFO                  | -      |

| EVALUA           | ATION                                                                  |        |

| 4.1 Pas          | ssive Optical technologies                                             | 63     |

| 4.2 Tin          | ne sensitive Ethernet                                                  | 63     |

|                  |                                                                        |        |

|                  | x-E Technology                                                         |        |

| 4.3.1            | Flex-E Testbed Implementation Description of HW –SW used               |        |

| 4.3.2            | Server Systems                                                         |        |

| 4.3.3            | Flex-E Routers                                                         |        |

| 4.3.4            | PTN990 Router features relevant to 5G-PICTURE                          |        |

| 4.3.4.           |                                                                        |        |

| 4.3.4.<br>4.3.4. |                                                                        | -      |

| 4.3.4.<br>4.3.4. |                                                                        |        |

| 4.3.4.           |                                                                        |        |

| 4.3.4.           |                                                                        |        |

| -                |                                                                        |        |

| 4.4 X-E          | thernet Platform Description                                           | 70     |

| 4.4.1        | Description of HW – SW used                                               | 71                           |

|--------------|---------------------------------------------------------------------------|------------------------------|

| 4.5 RF       | processing/modelling                                                      |                              |

| 4.5.1        | Sub-6 GHz LTE Massive MIMO coverage cell                                  |                              |

| 4.5.2        | mmWave Access Points (APs) along the trackside                            |                              |

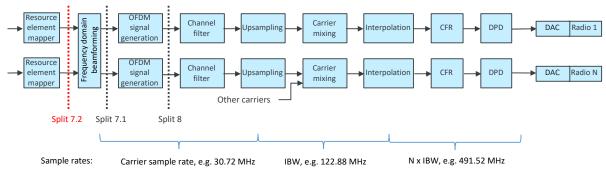

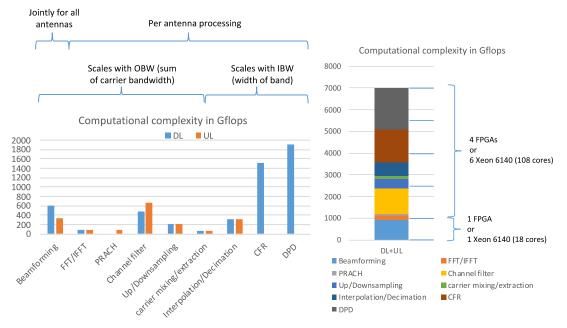

| 4.6 BB       | 3 Processing in Active Antenna Distributed Unit (AADU)                    | 77                           |

| 4.6.1        | Architecture Summary                                                      | 77                           |

| 4.6.2        | Functional Split: Computational Complexity                                | 78                           |

| 4.6.3        | AADU Configurability and Control                                          |                              |

| 4.7 M        | IMO at mmWaves                                                            |                              |

| 4.7.1        | LoS MIMO Theoretical Background                                           | 80                           |

| 4.7.1        |                                                                           |                              |

| 4.7.1        |                                                                           |                              |

| 4.7.2        | Experimental evaluation                                                   |                              |

| 4.8 Fu<br>86 | Illy programmable white-box edge device: experimental P4 use case for F-F | PU-5G performance evaluation |

| 4.8.1        |                                                                           |                              |

| 4.8.1        | L.2 Latency measurement                                                   |                              |

| 5 SUM        | MARY AND CONCLUSIONS                                                      |                              |

| 6 BIB        | LIOGRAPHY                                                                 |                              |

| 7 ACR        | RONYMS                                                                    |                              |

# List of Figures

| Figure 2-1: TSON edge node architecture.                                                                                               | . 14         |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 2-2: Structure of connection, frame and burst.                                                                                  | . 16         |

| Figure 2-3: Latency vs. Time slice duration (1500B, 5 Gb/s traffic).                                                                   | . 16         |

| Figure 2-4: Jitter (1500B, 5 Gb/s traffic).                                                                                            | . 17         |

| Figure 2-5: 10 Gb Ethernet High-Level Block Diagram.                                                                                   | . 18         |

| Figure 2-6: HPN Subsystem for synchronisation.                                                                                         | . 18         |

| Figure 2-7: Time stamp with HPN Subsystem for ingress and egress source node for loop-back scenario.                                   | . 18         |

| Figure 2-8: TSON extension for backhaul services with multi Ethernet clients                                                           | . 19         |

| Figure 2-9: Frame Structure.                                                                                                           | . 19         |

| Figure 2-10: CPRI frame structure over TSON.                                                                                           | . 20         |

| Figure 2-11: TSON edge node and CPRI integration high level architecture.                                                              | . 20         |

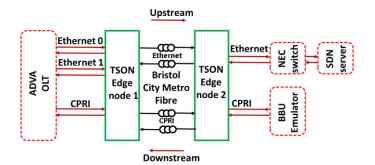

| Figure 2-12: TSON 5G-XHaul implementation architecture for 5G-XHaul final demonstration.                                               | . 21         |

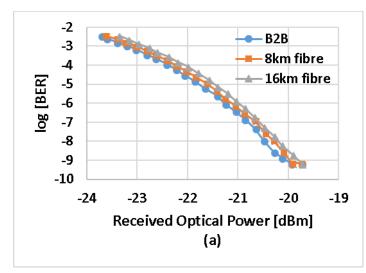

| Figure 2-13: Ethernet BER measurements.                                                                                                | . 22         |

| Figure 2-14: CPRI LCV measurements                                                                                                     | . 22         |

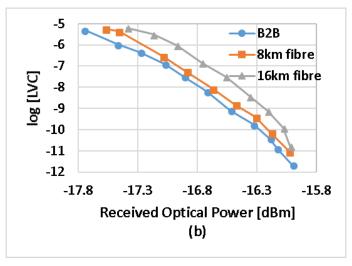

| Figure 2-15: TSON node1 CPRI reference clock and TSON node2 CPRI recovered clock                                                       | . 23         |

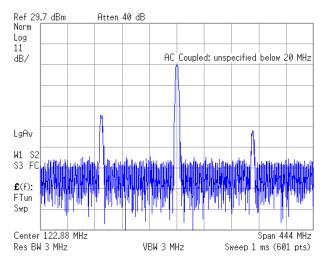

| Figure 2-16: CPRI recovered clock spectrum                                                                                             | . 23         |

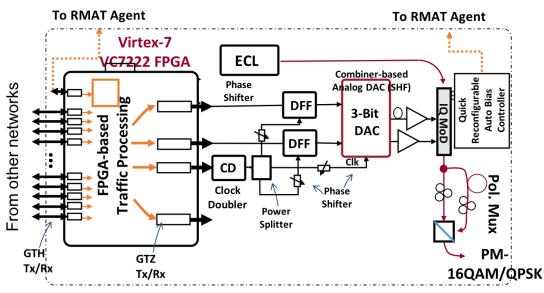

| Figure 2-17: Implementation of the modulation-adaptable transmitter                                                                    | . 24         |

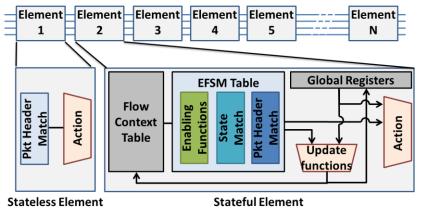

| Figure 2-18: OPP machine model.                                                                                                        | . 25         |

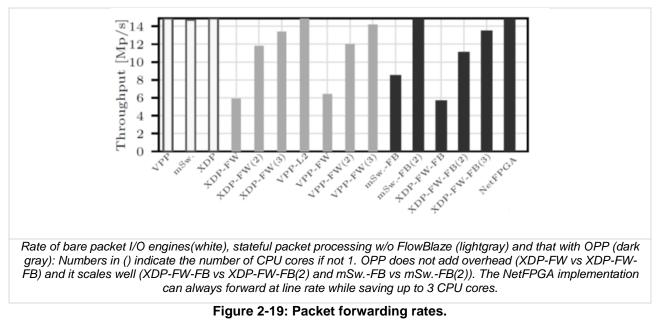

| Figure 2-19: Packet forwarding rates.                                                                                                  | . 26         |

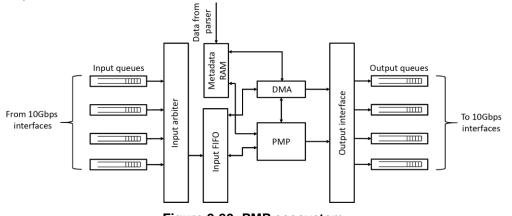

| Figure 2-20: PMP ecosystem.                                                                                                            | . 27         |

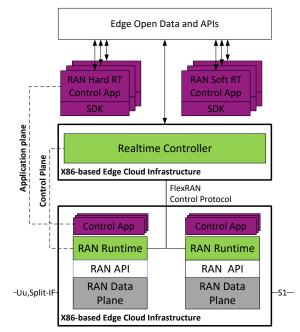

| Figure 2-21: OpenAirInterface and FlexRAN platforms                                                                                    | . 29         |

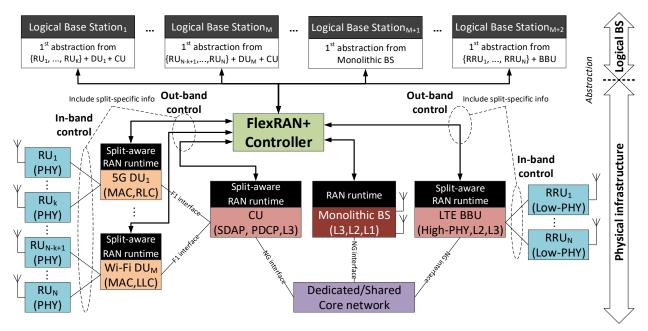

| Figure 2-22: Architecture of FlexRAN+ on top of a disaggregated RAN, exposing logical BS at the northbo<br>Interface                   |              |

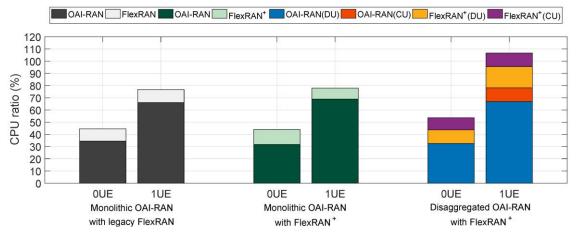

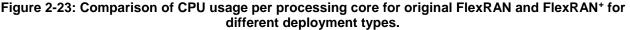

| Figure 2-23: Comparison of CPU usage per processing core for original FlexRAN and FlexRAN <sup>+</sup> for different deployment types. |              |

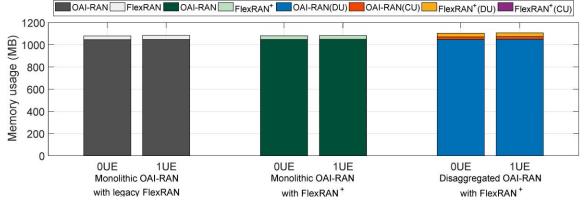

| Figure 2-24: Comparison of of memory usage for original FlexRAN and FlexRAN+ for different deploym types.                              | 1ent<br>. 33 |

| Figure 2-25: Point-to-Multi-Point single-hop scenario.                                                                                 | . 34         |

| Figure 2-26: digiBackBoard with the cooling and SMA adapters, Bottom and Top view.                                                     | . 34         |

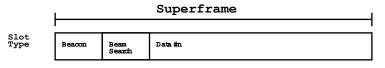

| Figure 2-27: Superframe structure with unified data slot for all devices.                                                              | . 36         |

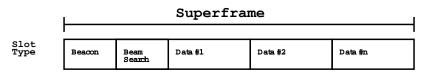

| Figure 2-28: Superframe structure with dedicated data slots per device.                                                                | . 36         |

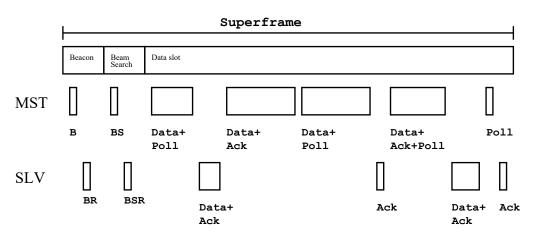

| Figure 2-29: Example of TDMA medium access during superframe and one unified data slot                                                 | . 36         |

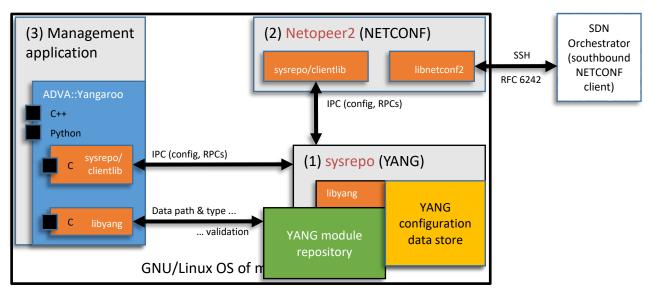

| Figure 2-30: ADVA NETCONF/YANG service implementation components.                                                                      | . 40         |

| Figure 3-1: PTP-based synchronisation control architecture.                                                                            | . 41         |

| Figure 3-2: PTP management message format.                                                                                             | . 42         |

| Figure 3-3: Management TLV                                                                                                             | . 42         |

| Figure 3-4: NETCONF architecture.                                                                                                      | . 45         |

|                                                                                                                                        |              |

### 5G-PICTURE Deliverable

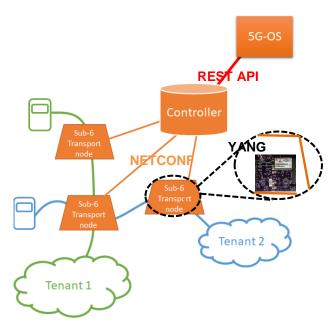

| Figure 3-5: example of multi-tenant Sub-6 GHz access/transport network                                                                                                                         | 47  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

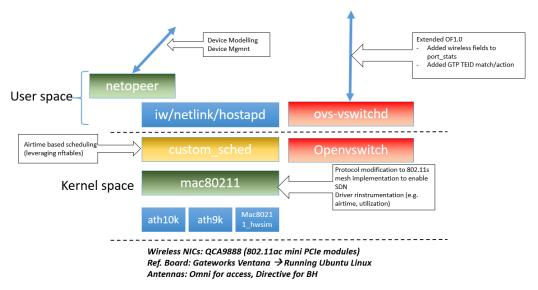

| Figure 3-6: Software architecture of the 5G-PICTURE Sub-6 GHz node.                                                                                                                            | 47  |

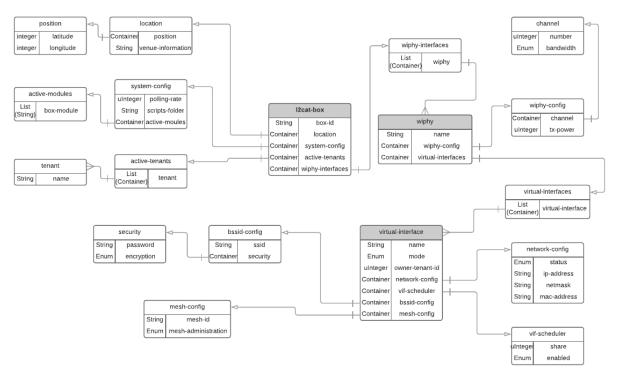

| Figure 3-7: YANG model of the I2cat-box.                                                                                                                                                       | 48  |

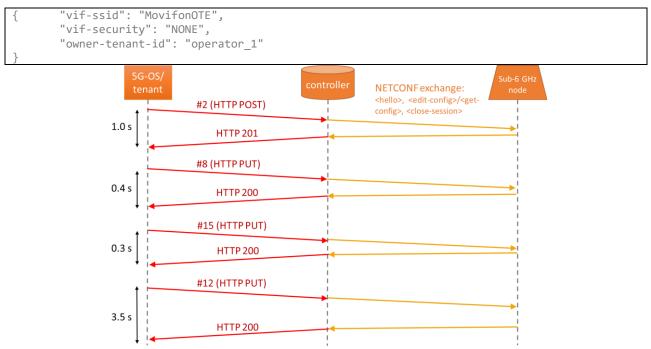

| Figure 3-8: Message exchange through northbound API                                                                                                                                            | 50  |

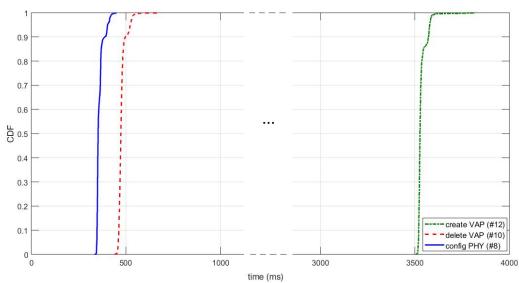

| Figure 3-9: Latency analysis (CDF of 1,000 runs) of three operations over Sub-6 GHz northbound API                                                                                             | 51  |

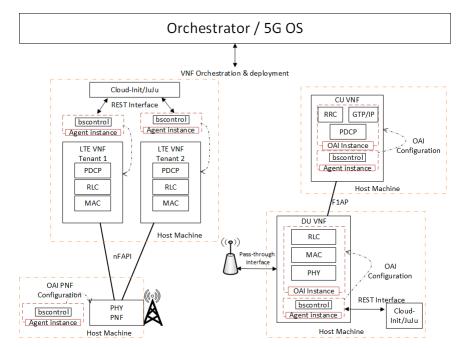

| Figure 3-10: Bootstrapping of different OAI VNFs through the bscontrol tool                                                                                                                    | 53  |

| Figure 3-11: Mellanox hybrid target pipeline.                                                                                                                                                  | 54  |

| Figure 3-12: Mellanox autogenerated APIs.                                                                                                                                                      | 55  |

| Figure 3-13: Mellanox P4 compilation flow                                                                                                                                                      | 56  |

| Figure 3-14: ADVA P4 Xilinx FPGA development workflow for F-PU-5G.                                                                                                                             | 57  |

| Figure 3-15: ADVA P4 Pipeline programming on F-PU-5G platform                                                                                                                                  | 58  |

| Figure 3-16: Example of XFSM rule entry.                                                                                                                                                       | 59  |

| Figure 3-17: XTRA lang workflow                                                                                                                                                                | 59  |

| Figure 3-18: Register declaration in XTRA lang                                                                                                                                                 | 59  |

| Figure 3-19: An example of macro-action declaration and call.                                                                                                                                  | 59  |

| Figure 3-20: The debug directive prints the value of the register "cwnd" every 500000 µs                                                                                                       | 60  |

| Figure 3-21: State definition in a typical XTRA lang program.                                                                                                                                  | 60  |

| Figure 3-22: An example of state declaration (slowStart), with an event (timeout) and two conditions in clause.                                                                                |     |

| Figure 3-23: An example of state marked as initial.                                                                                                                                            | 60  |

| Figure 3-24: The xtrac usage.                                                                                                                                                                  | 61  |

| Figure 3-25: A simple state with one event and two conditions. This will be translated in a single table e                                                                                     | -   |

| Figure 3-26: The JSON translation of the table entry in Figure 3-25.                                                                                                                           | 62  |

| Figure 4-1: Field-trial setup demonstrating multiple radio and split approaches over a converged time-sen<br>Ethernet link (inset: Breakdown of the prototyped 100G time-sensitive aggregator) |     |

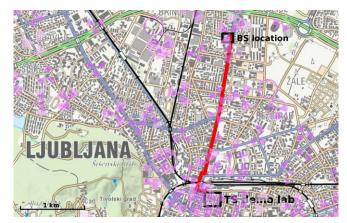

| Figure 4-2: Metro fibre link (in red) used in the field trial.                                                                                                                                 | 64  |

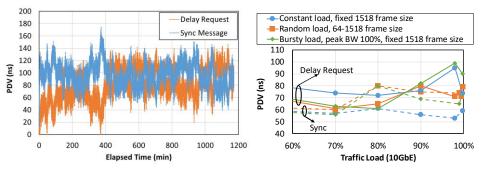

| Figure 4-3: Left: PDV analyses at the remote 1G and 10G ports. Right: PDV versus 10GbE load with diff traffic patterns.                                                                        |     |

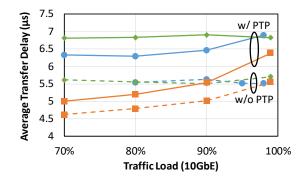

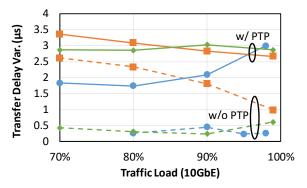

| Figure 4-4: Average round-trip transfer delay of SMTs.                                                                                                                                         | 65  |

| Figure 4-5: Transfer delay variation of SMTs.                                                                                                                                                  | 65  |

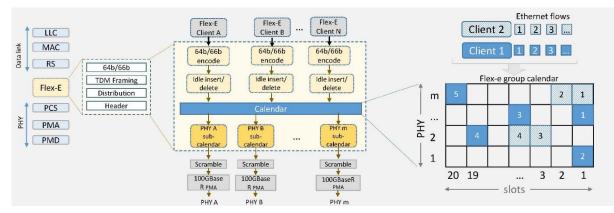

| Figure 4-6: Flex-E layer between Ethernet MAC and PCS. Additional FlexE Shim distribute/aggregate layer in PCS/PMD                                                                             |     |

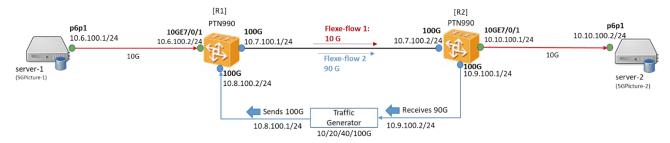

| Figure 4-7: Flex-E testbed logical view                                                                                                                                                        | 67  |

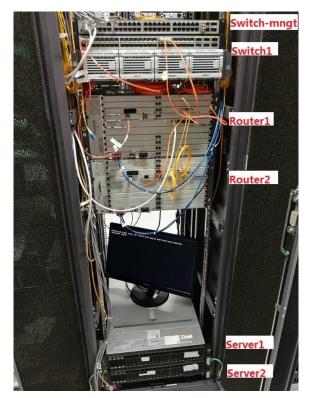

| Figure 4-8: Flex-E testbed                                                                                                                                                                     | 67  |

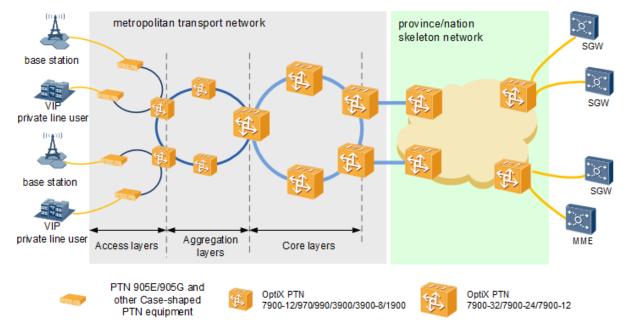

| Figure 4-9: OptiX PTN 990 networking on bearer networks and related functions.                                                                                                                 | 69  |

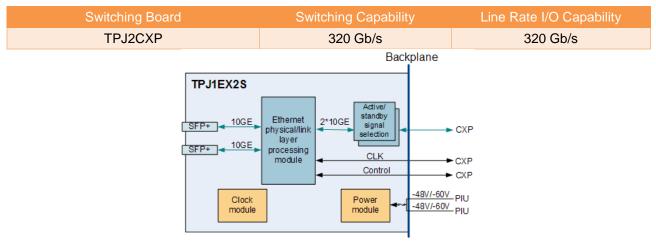

| Figure 4-10: Block diagram for the functions of the TPJ1EX2S                                                                                                                                   | 69  |

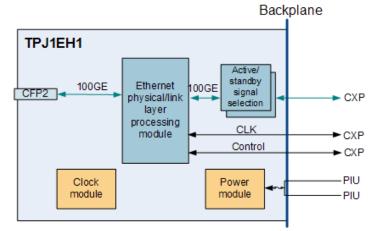

| Figure 4-11: Block diagram for functions of a TPJ1EH1                                                                                                                                          | 70  |

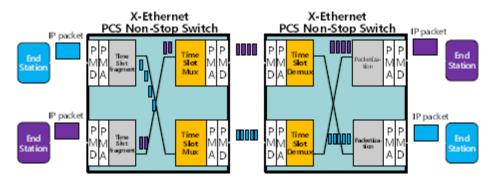

| Figure 4-12: X-Ethernet PCS NSS switching mechanism                                                                                                                                            | 71  |

| Figure 4-13: X-Ethernet prototype exterior.                                                                                                                                                    | 72  |

| H2020 ICT 2016 2017 762057 Dega <b>0 of 06</b> 20 Nov 2                                                                                                                                        | 010 |

| Figure 4-14: X-Ethernet FPGA board design.                                                                                                        | . 72 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 4-15: Windows side application software GUI                                                                                                | . 73 |

| Figure 4-16: Console interface.                                                                                                                   | . 73 |

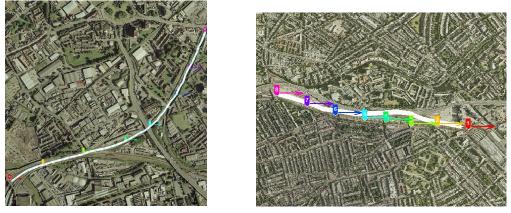

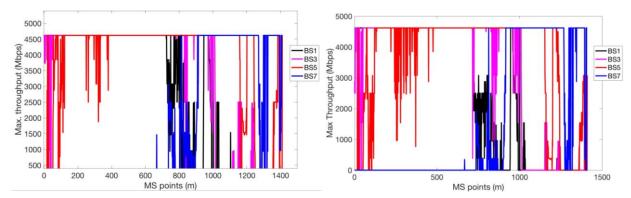

| Figure 4-17: LTE: Bristol Temple Meads scenario (a), London Paddington scenario (b)                                                               | . 74 |

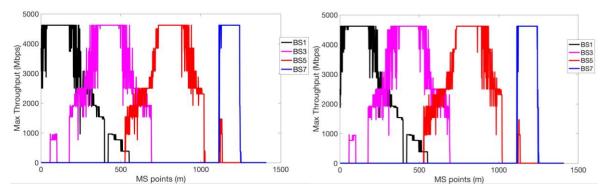

| Figure 4-18: LTE: P2P links, 2.6 GHz – Temple Meads: Max. Throughput (left), SNR (right)                                                          | . 74 |

| Figure 4-19: LTE: P2P links, 2.6 GHz – London Paddington: Max. Throughput (left), SNR (right)                                                     | . 75 |

| Figure 4-20: mmWave: Bristol Temple Meads scenario (left), London Paddington scenario (right)                                                     | . 75 |

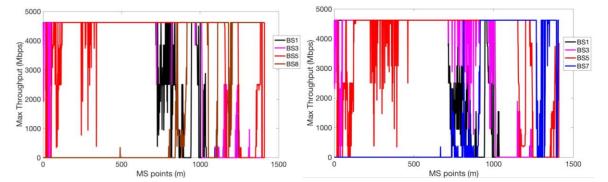

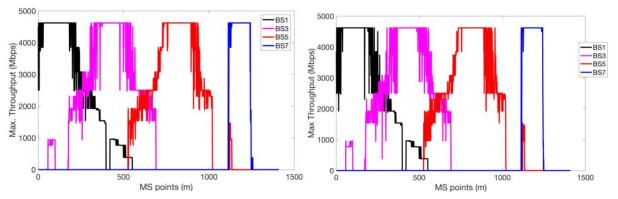

| Figure 4-21: Temple Meads - Throughput at 60 GHz without BF: (left) 7.5° bwidth (right) 10° bwidth                                                | . 76 |

| Figure 4-22: Temple Meads - Throughput at 60GHz with BF: (left) 7.5° bwidth (right) 10° bwidth                                                    | . 76 |

| Figure 4-23: Temple Meads - Throughput at 26GHz without BF: (left) 7.5° bwidth (right) 10° bwidth                                                 | . 76 |

| Figure 4-24: Temple Meads - Throughput at 26GHz with BF: (left) 7.5° bwidth (right) 10° bwidth                                                    | . 77 |

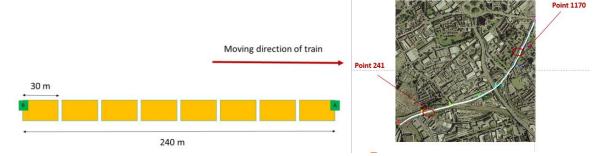

| Figure 4-25. (left) Train consideration in mmWave, (right) example of simulation in Temple Meads                                                  | . 77 |

| Figure 4-26: AADU processing chain and functional split.                                                                                          | . 77 |

| Figure 4-27: Computational complexity of PHY layer functions.                                                                                     | . 79 |

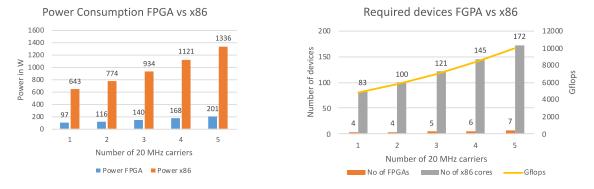

| Figure 4-28: Computational complexity: FPGA vs. x86                                                                                               | . 79 |

| Figure 4-29: Different antenna configurations for mmWave LoS MIMO.                                                                                | . 81 |

| Figure 4-30: LoS MIMO system                                                                                                                      | . 82 |

| Figure 4-31: Maximum achievable rate of the 60 GHz LoS MIMO system for different antenna configurati at 100 and 200 metres distances.             |      |

| Figure 4-32: (a) Diagram of the 2x2 MIMO setup and (b) receiver side of the 2x2 MIMO setup in the anech chamber showing the two AFEs and the RTO. |      |

| Figure 4-33: Post-processing of the recorded waveforms                                                                                            | . 85 |

| Figure 4-34: Power Spectral Density of received streams y1 and y2.                                                                                | . 85 |

| Figure 4-35: Equalised streams x1 and x2 (symbol-spaced) with rms EVM of 12.1 dB and 11.6 dB respectiv                                            |      |

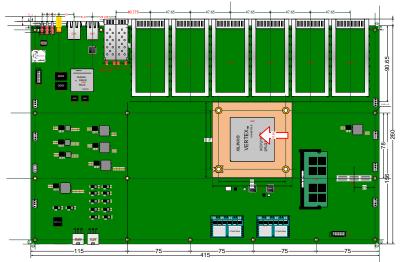

| Figure 4-36: F-PU-5G hardware layout.                                                                                                             | . 86 |

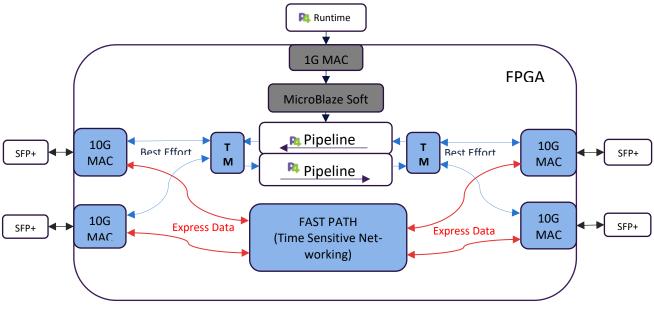

| Figure 4-37: FPGA architecture components involved in P4 use case on F-PU-5G.                                                                     | . 87 |

| Figure 4-38: FPGA layout for P4 use case on F-PU-5G.                                                                                              | . 87 |

| Figure 4-39: FPGA resource utilisation in P4 use case on F-PU-5G.                                                                                 | . 88 |

| Figure 4-40: FPGA resource utilisation of a single P4 Pipeline on F-PU-5G.                                                                        | . 88 |

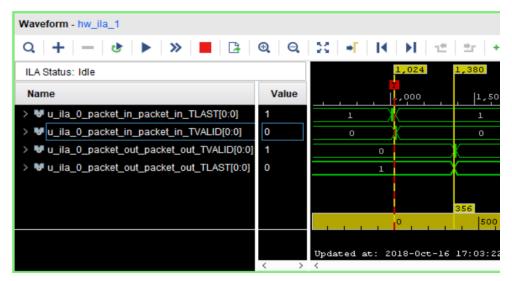

| Figure 4-41: Latency of a P4 Pipeline with one match-action table on F-PU-5G                                                                      |      |

| Figure 4-42: Latency of a P4 Pipeline with two match-action tables on F-PU-5G.                                                                    | . 89 |

# **List of Tables**

| Table 2-1: Ethernet upstream/downstream latency                                                                                            | 22 |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2-2: CPRI upstream/downstream latency                                                                                                | 23 |

| Table 2-3: Parameters of an OPP stateful element in our hardware implementation                                                            | 25 |

| Table 2-4: NetFPGA's resource requirements for OPP with a single stateful element compared to the reference, single-stage Ethernet switch. |    |

| Table 2-5: Synthesis results                                                                                                               |    |

| Table 2-6: Comparison of FlexRAN and FlexRAN+ characteristics                                                                              | 32 |

| Table 2-7: Configuration of PTMP-MAC                                                                                                       | 35 |

| Table 2-8: Example of beam search algorithm for the link establishment procedure                                                           |    |

| Table 3-1: PTP data sets and read operations                                                                                               | 43 |

| Table 3-2: commands for network programmability and synchronisation.                                                                       | 43 |

| Table 3-3: dynamic attributes for which a dedicated management message is not defined                                                      | 45 |

| Table 3-4: operations on the REST API-based northbound interface of the Sub-6 GHz portion                                                  | 48 |

| Table 4-1: Server HW specification                                                                                                         | 68 |

| Table 4-2: Switching capability of the OptiX PTN 990                                                                                       | 69 |

| Table 4-3: mmWave: Modelling and analysis parameters                                                                                       |    |

| Table 4-4: mmWave LoS MIMO: optimal antenna spacing                                                                                        | 81 |

| Table 4-5: mmWave LoS MIMO: simulation parameters                                                                                          | 83 |

| Table 4-6: mmWave LoS MIMO: results.                                                                                                       | 83 |

| Table 4-7: Latency impact of match-action tables in P4 Pipelines on F-PU-5G                                                                |    |

## **Executive Summary**

This document corresponds to deliverable D3.2, entitled "Intermediate report on Data Plane Programmability and infrastructure components" of the H2020 5G-PICTURE project. The deliverable provides the detailed functional definition of the programmable platforms that are being developed within 5G-PICTURE's WP3 activities, the implementation results and a preliminary evaluation of the performance achievable with the developed platforms.

To exploit the programmability of these platforms a set of suitable hardware abstractions has been developed. The description of these abstractions, an initial performance assessment and their functional evaluations are reported as well in this deliverable.

The final description of the developments implemented in each of the programmable platforms, together with the performance evaluations and will be provided in deliverable D3.3, with due date November 2019.

### 1 Introduction

As stated in deliverable D3.1, the 5G-PICTURE vision of a disaggregated hardware/software (HW/SW) allocation of network functionalities in different nodes of the network providing different resource types requires a significant increase in the programmability and flexibility of these nodes. We focused on the development of programmable platforms as an enabler to deploy into the network different functionalities that can be specified using certain high level description and be deployed at run-time on specific platforms. The network operating system should be able to estimate the performance achievable with the different platforms and to allocate in the most suitable node the network function that must be executed. This approach will permit the 5G network to support a wide set of complex network functionalities, which can be dynamically changed and moved among different network nodes depending on the network conditions (traffic, faults, link availability, etc.) and on the required Service Level Agreements (SLAs). Furthermore, programmability is also a mandatory element to permit the adoption of new protocols/services that could come up in the future.

The other element on which the WP3 tasks are focused on is efficiency of the developed programmable platforms. While it is fairly simple to provide programmability and flexibility sacrificing performance, it is much more challenging to achieve a greater programmability level without sacrificing the performance. Therefore, the 5G-PICTURE project focused the effort of WP3 in designing efficient programmable platforms. In the previous deliverable several common aspects that the programmable platforms of the different network domains (ethernet, optical, and radio access) has been identified: (i) the programmable network platforms must provide clear programming models that will allow development of network functions (NFs), decoupling the definition of the function from the specific platform-dependent implementation. Possible programmable dataplanes or the OpenCL language for the definition of digital signal processing (DSP) radio functions; (ii) the control/data plane separation enabled by the use of SDN technologies that is dominating the wired network scenario can be extremely useful also in the radio and optical network domains; (iii) a set of hardware abstractions and/or interfaces are needed to provide an API that can be used for configuring the programmable platforms.

This deliverable presents the current status of the work related to the development of the interfaces, programming models, and hardware abstractions of the programmable network platforms that are under development in the 5G-PICTURE project.

#### Organisation of the document

This deliverable is structured as follows: Section 2 presents the detailed functional definitions of the programmable platforms that are under development and an initial evaluation of the performances achievable with the proposed platform. A definitive assessment of the performances will be provided in the deliverable D3.3.

Section 3 presents the hardware abstractions that are used to decouple the details of the programmable platforms implementation from its configuration capability.

Section 4 illustrates the different hardware technologies developed in 5G-PICTURE that provide basic building blocks of the 5G network architecture, comprising novel optical as well as RF and baseband (BB) processing technologies.

Finally, section 5 contains the summary and conclusions.

## 2 Functional definition of programmable platforms: implementation results and preliminary evaluation

This section reports the progresses of Task 3.1. The main goal of this task is to emerge with domain-specific processors which pre-implement (very efficiently, e.g. in HW) functional primitives reusable by multiple network functions. In the first phase of Task 3.1 the consortium focused on the architectural definition of the programmable platforms. The second phase of this task focused on the detailed implementation of these platforms and an initial evaluation of the performance achievable with the associated technologies. In particular, for the backhaul (BH), the platforms will provide a highly *programmable stateful dataplane* with latency and throughput performances able to sustain the need of the 5G network. For the fronthaul (FH), reconfigurable HW platforms will be used to provide both *SDN-based programmability* and efficient allocation of the processing tasks with flexible *functional splitting* between the radio units (RUs) and the base station (BS).

#### 2.1 Time-Shared Optical Network (TSON) Platform

The 5G-PICTURE solution uses the Time-Shared Optical Network (TSON) technology [20], which provides programmable converged fronthauling/backhauling functions and offering suitable multi-technology, multi-protocol interfaces based on FPGA-based programmable HW.

#### 2.1.1 Generic TSON functionality/architecture, capabilities, and evaluation results

This subsection briefly recall the generic TSON functionality already introduced in deliverable D3.1 [1] and presents the resource allocation capabilities and the initial TSON evaluation results. In addition, a description of the Real-Time Bandwidth Variable Optical Transmitter is provided in this section.

#### 2.1.2 Generic TSON functionality/architecture

TSON is a multi-wavelength fully bi-directional synchronous and novel frame based flexible system. It delivers a flexible and statistically multiplexed optical network infrastructure able to support on-demand guaranteed time-shared multi-granular services. Its network implementation consists of field-programmable gate array (FPGA) optoelectronics platforms integrated with advanced optical components to enable high performance processing and transparent switching and transport [20] [21] [22]. TSON is a contention-less solution through the deployment of a central resource allocation engine of route, wavelength, and time assignment, responsible to set-up paths of sub-wavelength granularity.

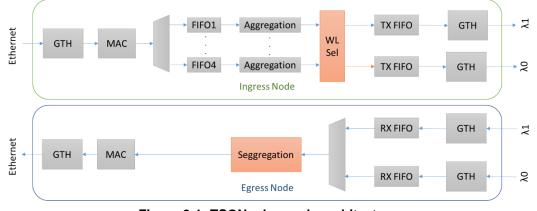

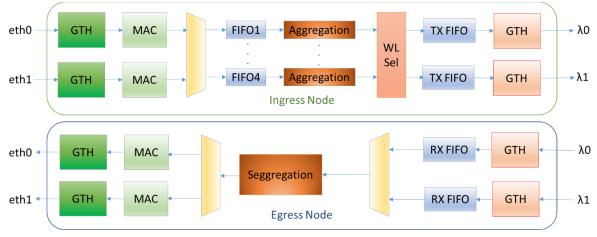

The TSON solution includes two different types of nodes, the edge and the core nodes, incorporating different functionality and level of complexity. TSON edge nodes provide the interfaces between wireless, Passive Optical Network (PON) and Data Centre (DC) domains to the optical TSON domain and vice versa. Figure 2-1 shows the TSON edge architecture. The ingress TSON edge nodes are responsible for traffic aggregation and mapping, while the egress edge nodes include the reverse functionality. To send and receive data, each TSON edge node uses four SFP+ transceivers, two 1310 nm 10 km reach for end-point server traffic and control, and two DWDM 80 km reach transceivers at 1544.72 nm and 1546.12nm. The 1310 nm interfaces can be used to support both data and control traffic either separately or combined depending on whether out-off band or inband control is adopted. For more information on the TSON overall architecture and interfaces the interested reader is referred to 5G-XHaul deliverable D2.2 [23].

### 5G-PICTURE Deliverable

When the ingress part of the edge node receives traffic, the FPGA waits to finish the processing of the current frame, and then starts to transmit time-slices by assigning optical bandwidth to these. The optical bandwidth allocated to the different services is not fixed but can be elastically defined based on the requirements of each service. Therefore, TSON can support elastic time and optical bandwidth allocation. As an example, in Figure 2-1, when the input traffic comprises Ethernet frames at the ingress part of the edge node, the Ethernet frames received at the 10 Gb/s receiver are passed to the 10GE Medium Access Control (MAC); Then MAC discards the preambles and Frame Check Sequence (FCS), transmits the data to the Receiver (RX) in a first in first out (FIFO) manner and indicates whether the packet is good or not; the RX FIFO receives the data, waits for the good/bad indication from the MAC, and sends it to the DEMUX block if there is any valid data. The DEMUX analyses the Ethernet frame information (i.e. Destination MAC address, Source MAC address, etc.) and puts them in a different FIFO. After that, the FIFO does not send any data until the AGGREGATION gives a command; the register file of AGGREGATION, containing the Time-slice Allocation information, is updated by the Lookup Table (LUT) (this table stores information related to time-slice Allocation and the fast-optical switch that is incorporated in the edge TSON node). The AGGREGATION module waits until the burst-length Ethernet frames are ready in the FIFO and the time-slice allocation is available, then it transmits the bursts with a suitable wavelength through the TX FIFO. For the egress part of the edge TSON node, when the 10 Gb/s receiver receives a burst (time-slice), it drops the burst in the RX FIFO Lambda0/Lambda1; after the burst is completely received, the SEGREGATION block segregates the burst to Ethernet frames and transmits them to a TX FIFO. Every time the TX FIFO receives a complete Ethernet frame it sends it to the 10GE MAC. Finally, MAC passes the data to the 10 Gb/s transmitter and transmits them out.

The TSON core nodes do not carry out any data processing but need to switch the traffic optically. Therefore, the FPGA-based TSON core node controls the fast-optical switches to setup the path with a client's request. These nodes switch transparently the optical frames to the appropriate output port utilising the fast-optical switching which in the core node as was also in the edge node case. The TSON core nodes adopt the wave-length selective architecture and as such require one switch per wavelength, to direct the incoming optical time-sliced signals towards the appropriate output ports, as defined by the control plane. The dimension of the space switch is defined by the number of fibres that are interconnected through the node. The TSON core node uses the same type of high performance FPGA boards for the ((Pb,La)(Zr,Ti)O3) (High-Speed PLZT Optical Switches) control. The FPGA LUTs are filled in by the control plane, through customised Ethernet communication carrying PLZT switching information, to be able to change the switch state per time-slice on the PLZT switches with the aim to establish and maintain optical paths across the TSON domain. The basic functions for the operation of TSON domains have been implemented in internal modules, within the Software Defined Networking (SDN) controller, that cooperates for the on-demand provisioning of connectivity between TSON core and edge nodes. The interested reader can find a detailed description of the TSON control plane in the 5G-XHaul deliverable D3.1 [24].

TSON works in two different modes: Ethernet and Elastic bandwidth allocation mode. The Ethernet mode is for Ethernet-based packets without any time-slicing. Elastic bandwidth allocation is based on time-slicing as described earlier in this section. Even though the latest TSON implementation is based on Xilinx Virtex7 board (156.25 MHz clock frequency), supporting multiple 10 Gb/s (for control and transport) DWDM SFP+ transceivers, the architecture can support rates beyond the 10 Gb/s (i.e. 25, 40, 100 Gb/s). For the optical layer, TSON relies on fast optical PLZT switches [22] having 10 ns switching speed as well as a set of active and passive components including Erbium Doped Fibre Amplifiers (EDFAs), MUX/DEMUXes, etc. TSON is designed and implemented as a novel frame-based, time multiplexing network solution, offering dynamic connectivity with fine granularity of bandwidth.

Although natively TSON allows handling of Ethernet frames, its configuration can support a broad range of framing structures and communication protocols including CPRI and Open Base Station Architecture Initiative (OBSAI), either natively or through their packetised versions.

#### 2.1.3 TSON resource allocation capabilities

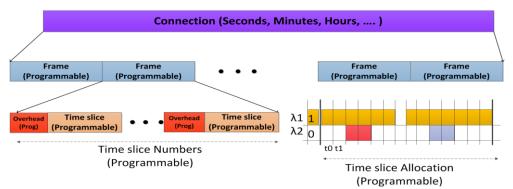

TSON is fully SDN enabled, and the parameters of TSON nodes are programmable by the controller, such as Quality of Transmission (QoT), overhead that is programmable from 0 to 39 KB, time-slice size that is programmable from 80 B to 31.25 KB, time-slice numbers in a frame that are programmable from 4 to 100, and time-slice allocation. Thus, when the client (e.g. operator, service provider) requests to setup a network service, after evaluating its requirements such as bit-rate, connectivity type, Quality of Service (QoS), and QoT by the network controller, the TSON nodes chose the corresponding QoT overhead size, Time-slice size, time-slice

number and time-slice allocation to fulfil such requests to compose a dedicated network function slice of the node. In addition, TSON supports programmable traffic flow control (i.e. VLAN, Dest MAC, Src MAC).

TSON offers a hierarchy of three levels of resource granularity: connections, frames, and time-slices, as illustrated in Figure 2-2. Connection refers to a sub-wavelength light path establishment between any two end points in the TSON domain. To improve statistical multiplexing of data units, each connection lasts for a number of frames and the minimum duration of 1ms. Each frame is divided into time-slices as the smallest units of network resources, i.e. the actual sub-lambda resources. The frame length and the number of time-slices inside a frame define the minimum granularity achievable by the TSON network [23]. The TSON framework offers a very flexible optical platform that supports sub-wavelength switching, frame lengths, varying from 64 ns to 25.6 µs and variable bit rates, spanning from of 30 Mb/s up to several Gb/s, with 30 Mb/s step.

#### 2.1.4 Generic TSON Evaluation

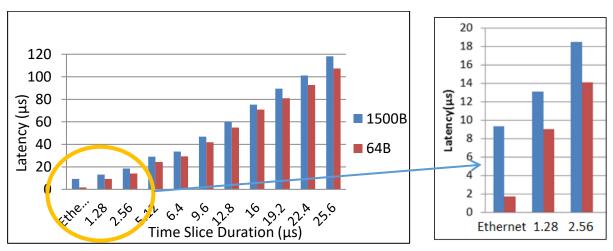

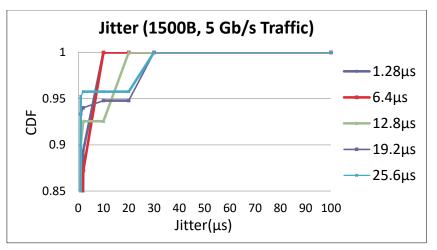

Figure 2-3 and Figure 2-4 show the TSON evaluation results obtained using Ethernet as an interface technology. This evaluation is based on latency and jitter analysis.

Figure 2-3 displays the impact of latency as a function of time-slots. As expected, the latency increases as the time-slice size increases because a higher number of packets are accumulated in a given time-slot. However, when the TSON node is in the Ethernet mode the minimum latency is  $1.747 \ \mu$ s, while when it is in Elastic bandwidth allocation mode, the latency ranges from  $9.234 \ \mu$ s to  $118.233 \ \mu$ s.

On the other end, Figure 2-4 shows the impact of jitter as a function of time-slices. The frame size is set to 1500B with 5 Gb/s traffic. As the time-slice size grows, the percentage of traffic not received in a given time (e.g.,  $2 \mu$ s) decreases, but the percentage of traffic with more latency increases, thus increasing the jitter.

The minimum latency is 1.747  $\mu$ s, while, in Elastic Time Division Multiplexing (TDM) mode, the latency ranges from 9.234  $\mu$ s to 118.233  $\mu$ s when the node is in Ethernet mode. In addition, as the time-slice duration increases, so does the jitter, and the number of packets not received at certain times increases.

Figure 2-2: Structure of connection, frame and burst.

Figure 2-3: Latency vs. Time slice duration (1500B, 5 Gb/s traffic).

Figure 2-4: Jitter (1500B, 5 Gb/s traffic).

#### 2.2 TSON extensions provided in support of FH and BH services

TSON was proposed as a suitable optical transport technology in support of BH and FH services. However, the initial TSON implementation needed several extensions to become suitable to support FH and BH services. These extensions that are currently being further enhanced were originally implemented in the framework of the Phase 1 5G-PPP project 5G-XHaul and included synchronisation, support of multi Ethernet clients for backhaul, and CPRI integration for FH services.

#### 2.2.1 TSON Synchronisation

To achieve high synchronisation accuracy over the network, accurate timestamps are required. Although TSON has its own synchronisation scheme [23], the TSON network requires global frame synchronisation among TSON nodes to meet the precision needed in the 5G-PICTURE project environment. This solution takes advantage of the IEEE-1588 v2 protocol [25] across heterogeneous domains. This solution needs to be at least a Transparent Clock (TC) for a given domain/node. This introduces the following requirements:

- The domain/node can measure the residence time of a 1588v2 packet inside the domain/node. This indicates: 1588 packets are recognised at the ingress, a timestamp is generated in the node, at the egress port the time is again measured, a residence time is computed "as egress-ingress time".

- The residence time is copied in a subsequent "Follow up" packet sent by the 1588 Master clock node.

- The synchronisation end-point will subtract the residence time from the follow up to this measurement of RTT in order to remove per domain jitter.

Applying the approach described above to a TSON domain means that the residence time is computed at the egress TSON node as the difference between its current time and the time when the packet enters the TSON ingress source node. Therefore, the TSON nodes need to be synchronised being, in principle, a different synchronisation to that of 1588 v2. It is a synchronisation local to TSON that requires it to be able to compute the residence time in a meaningful way. In this scenario, the ingress time needs to be conveyed to the TSON egress node. Therefore, the time stamps need to be transmitted in-band to calculate the residence time.

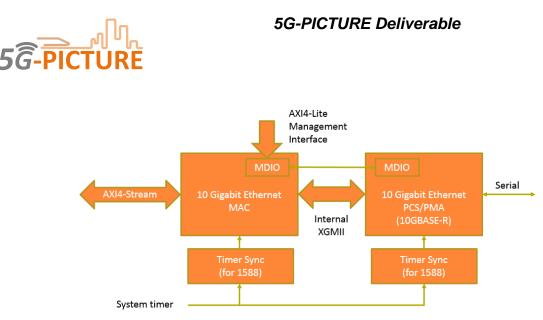

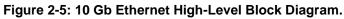

As TSON is FPGA based programmable HW, Xilinx 10 Gigabit Ethernet Subsystem IP core [26] supports high accuracy IEEE-1588-v2 1-step and 2-step timestamping on a 10GBASE-R network interface. Figure 2-5 shows the block diagram of the 10G Ethernet MAC subsystem. The subsystem IP core has three main sub IP cores: a MAC, a Physical layer - Physical Coding Sublayer (PCS)/ Physical Medium Attachment (PMA), and a Timer for synchronisation. The time stamper unit for the transmit-side and the receiver-side are implemented inside the MAC and the PCS/PMA sub IP cores, respectively.

This subsystem synchronises the 1588 system timer in the selected format from the system timer clock domain into the subsystem clock domain for each of the transmit and receive data paths. This guarantees high accuracy for the 1588 timestamps. The selected format is available in one of two Time-of-Day (ToD) and Correction Field timestamp formats. The subsystem supports both In-band and out-of-band timestamping methods. The system timer could be delivered to the FPGA board via available SubMiniature version A (SMA) user clock on the board.

Xilinx subsystem IP core does not support multiple IEEE-1588 v2 enabled subsystem instances [27]. In addition, as we mentioned before, the residence time needs to be computed at the egress TSON node as the difference between its current time and the time when the packet enters the TSON ingress source node. Therefore, the TSON nodes need to be synchronised and this in principle is different synchronisation than the synchronisation carried out by IEEE-1588 v2 even though the timing format – i.e. Time of Day (ToD) and Correction Field – is the same as in IEEE-1588 v2.

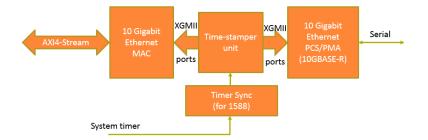

To resolve this problem and the Xilinx IP core limitation, a new subsystem, called HPN subsystem, has been developed to support multiple IEEE-1588-v2 enabled subsystem. As it was mentioned before, the Xilinx approach uses a time stamper unit for the transmit-side and the receiver-side inside the MAC and the PCS/PMA sub IP cores, respectively. Unlike the Xilinx approach, the developed HPN subsystem uses a separate developed time stamper. Figure 2-6 shows the HPN subsystem architecture. The HPN time stamper follows the same features as the Xilinx subsystem. The time stamper unit is located between the MAC and PCS/PMA IP cores, uses the Timer Sync clock and follows the IEEE 1588 protocol. In addition, the time stamper considers the physical layer delay for stamping. Figure 2-7 shows the captured waveform of both transmit and the receiver sides after time stamping for loop-back case. In this scenario, the ingress and egress time stamps are both the same as the ones we used in the loop-back approach and therefore the residence time is zero.

Figure 2-6: HPN Subsystem for synchronisation.

| <mark>∥₀</mark> gtx_dk           | 1                  |      |      |             |                 |                  |     |         |        |     |              |   |                                         |     |           |         |        |              |

|----------------------------------|--------------------|------|------|-------------|-----------------|------------------|-----|---------|--------|-----|--------------|---|-----------------------------------------|-----|-----------|---------|--------|--------------|

| 🔓 xgmii_tx_dk                    | 0                  |      |      |             |                 |                  |     |         |        |     |              |   |                                         |     |           |         |        |              |

| 📲 xgmii_txd[63:0]                | 070707070707070707 |      |      |             |                 | 7070707070707070 | 7   |         |        |     |              | D | 00000000000                             | 00  | 000000    | 000000. | 000    | 0000000000.  |

| 📲 xgmii_txc[7:0]                 | ff                 |      |      |             |                 | ff               |     |         |        |     |              | X | 00                                      |     | 0         | d       |        | 00           |

|                                  | 1                  |      |      |             |                 |                  |     |         |        |     |              |   |                                         |     |           |         |        |              |

| <mark>" (</mark> xgmii_rxd[63:0] | 000000001a10a655   | 0000 | 000  | 0000000000  | 000000000000000 | 000000000        | 000 | 000000  | 000000 | 000 | 0000000000 ) | 0 | 000000000000000000000000000000000000000 |     | 000000000 | 000     | 00000  | 0000000 )    |

| 🙀 xgrvc[7:0]                     | 00                 | 00   |      | 00          | 00              | 00               |     | 00      |        |     | 00           |   | 00                                      | DK  | 00        |         |        | <b>0</b> 0 ) |

| lingtx_dk                        | 1                  |      |      |             |                 |                  |     |         |        |     |              |   |                                         |     |           |         |        |              |

| xom=_u_ak                        | 1                  |      |      |             |                 |                  |     |         |        |     |              |   |                                         |     |           |         |        |              |

| (xgmi_txd[63:0]                  | 00000000 1a 10a655 |      |      |             |                 | 7070707070707070 | 7   |         |        |     |              | D | 00000000000                             | 00_ | 0000000   | 00000.  | 000    | 0000000000.  |

| xgini_tvc[7:0]                   | 00                 |      |      |             |                 | ff               |     |         |        |     |              | Х | 00                                      |     | 0         | ,       |        | 00           |

| a xgmii_rx_dk                    | 1                  |      |      |             |                 |                  |     |         |        |     |              |   |                                         |     |           |         |        |              |

| 🖥 xgmii_rxd[63:0]                | 0000000000000000   | 0000 | 0000 | 000000000 ) | 00000000000000  | 000000000        | 000 | 0000000 | 00000  | 000 | 0000000000   | 0 | 000000000000                            |     | 000000000 | 000     | 000000 | 0000000 )    |

| 🖬 xgmii_rxc[7:0]                 | 00                 | 00   |      | 00          | 00              | 00               |     | 00      |        |     | 00           |   | 00                                      |     | 00        |         |        | 00           |

Figure 2-7: Time stamp with HPN Subsystem for ingress and egress source node for loop-back scenario.

Figure 2-8: TSON extension for backhaul services with multi Ethernet clients.

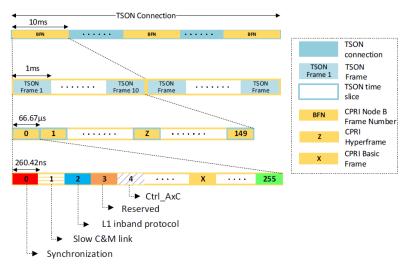

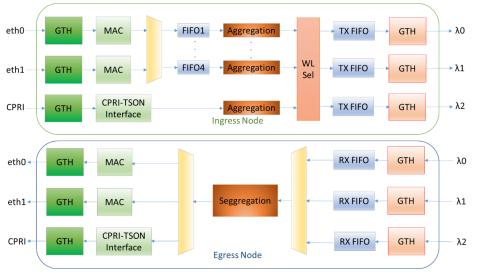

#### 2.2.2 Backhaul Services over TSON – Supporting Ethernet

Extension of the TSON clients are only limited to the number of available transceivers on FPGA boards. We extended the TSON Ethernet client ports to support BH services.

Figure 2-8 shows the extended TSON solution to support BH service requirements in 5G. The multi-line client TSON follows the one client TSON legacy when the clients are using a different wavelength (i.e.  $\lambda$ ). In addition, the Ethernet clients can use a common wavelength if the total bandwidth of the clients is less than 10 Gb/s. In this scenario, the packets are delivered to the related Ethernet clients at the egress nodes based on their header information (VLAN tag for 5G-XHaul [24]).

#### 2.2.3 FH Services over TSON – CPRI extension

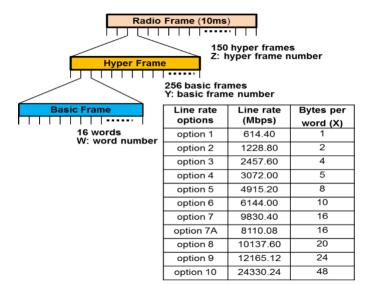

Figure 2-9 shows the CPRI frame structure that sends sampled In-phase Quadrature (IQ) data in a frame format. The CPRI radio frame is 10 ms. CPRI line rate information is sent in Z.Y.W.X format between the RU and the Baseband Unit (BBU), where Z is the hyper frame number, Y is the basic frame within a hyper frame, W is the word number within a basic frame, and X is the byte number within a word. A single basic frame duration is 260 ns (1/3.84 MHz) which is compatible to a Universal Mobile Telecommunications System (UMTS) chip length. Each basic frame consists of 16 words, and the word length depends on the CPRI line rate: 256 basic frames make a hyper frame, and 150 hyper frames make a radio frame. CPRI supports topologies such as tree, ring, and chain, each link between RU and BBU is a fixed-bandwidth TDM connection.

Figure 2-9: Frame Structure.

Figure 2-10: CPRI frame structure over TSON.

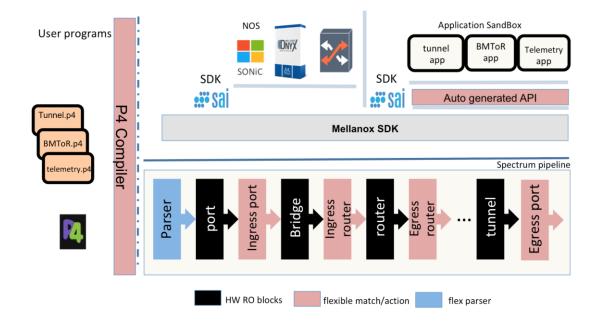

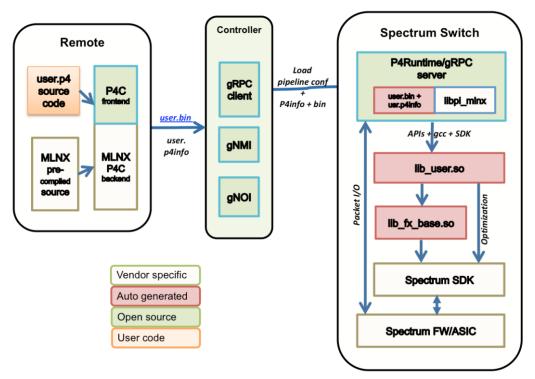

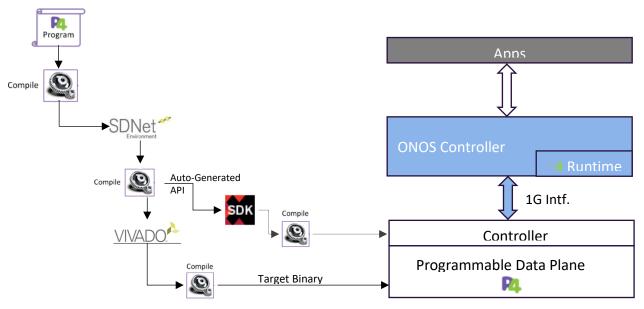

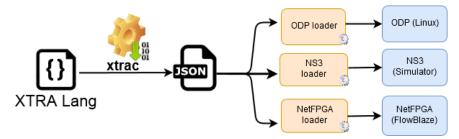

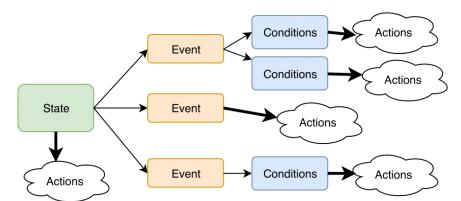

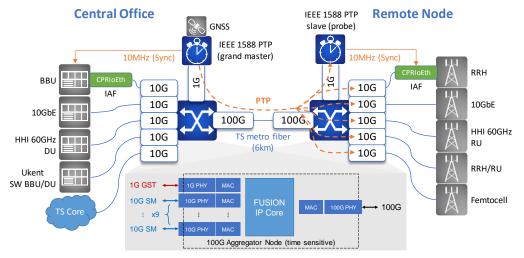

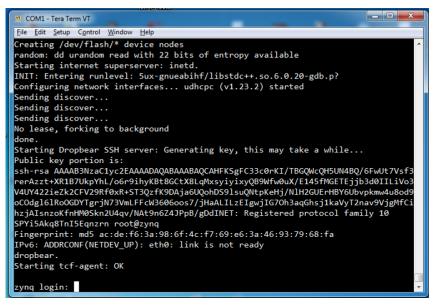

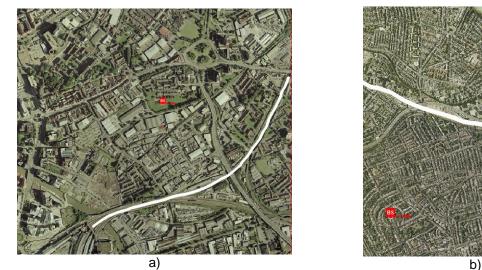

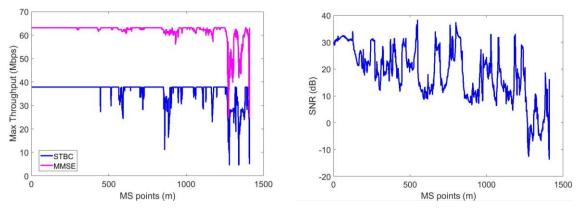

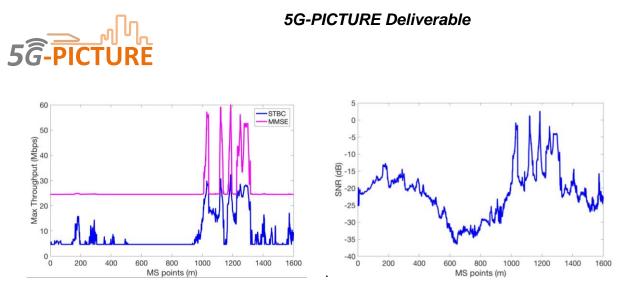

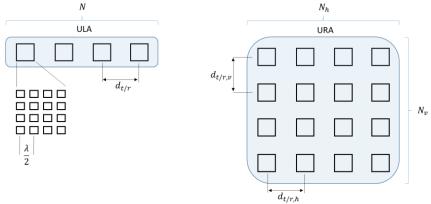

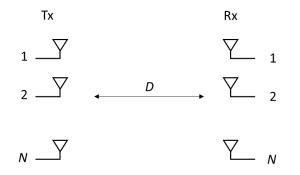

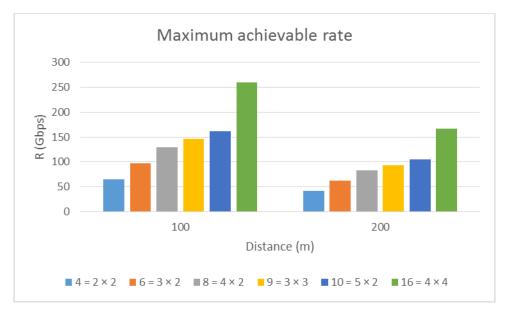

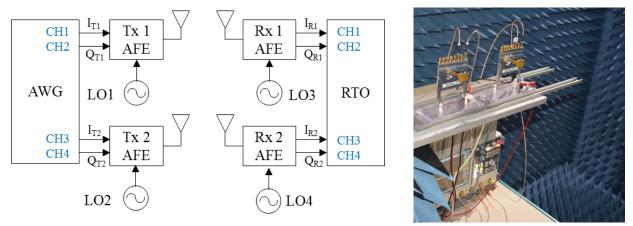

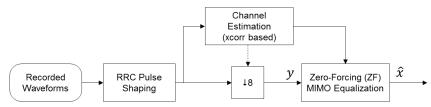

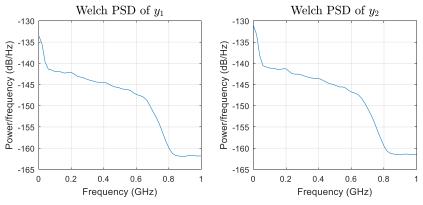

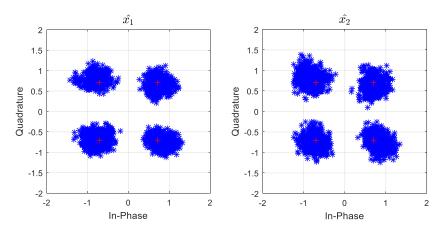

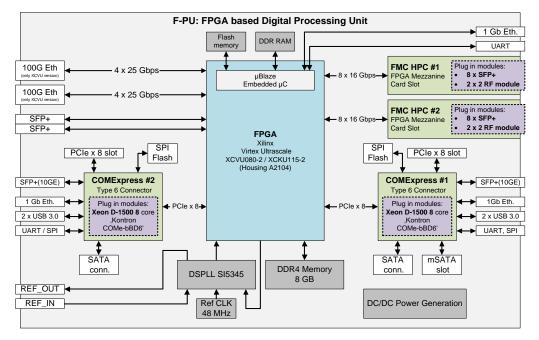

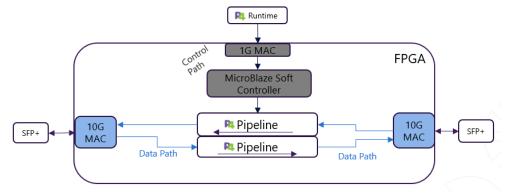

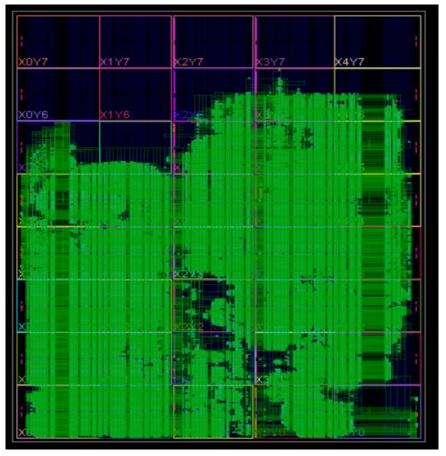

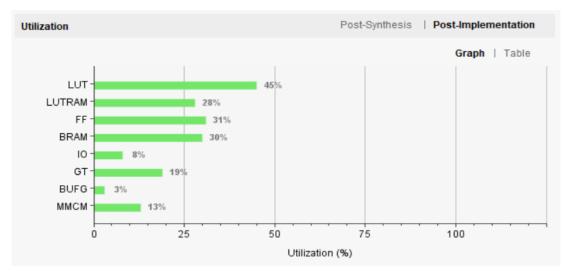

TSON's extension to enable native CPRI can support up to line rate option 5 with the current implementation as in 5G-XHaul the BBU and the Remote Radio Head (RRH) are using this option. The higher line rate option could use the same methodology for the TSON-CPRI integration. TSON can support varying service related requirements as its operational characteristics can be dynamically modified. Figure 2-10 illustrates how a heavy CPRI flows can be embedded into the TSON framing structure.