Horizon 2020 European Union funding for Research & Innovation

5G Programmable Infrastructure Converging disaggregated network and compUte REsources

# D3.1 Initial report on Data Plane Programmability and infrastructure components

This project has received funding from the European Union's Framework

Programme Horizon 2020 for research, technological development and

demonstration

5G PPP Research and Validation of critical technologies and systems

Project Start Date: June 1<sup>st</sup>, 2017

Duration: 30 months

Date of delivery: March 31<sup>st</sup> 2018 <u>April 4<sup>th</sup> 2018</u>

**Topic:** ICT-07-2017

Call: H2020-ICT-2016-2

Project co-funded by the European Commission Under the H2020 programme

Dissemination Level: Public

Version 1.0

### 5G-PICTURE Deliverable

| Grant Agreement Number: | 762057                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project Name:           | 5G Programmable Infrastructure Converging dis-<br>aggregated network and compUte REsources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Project Acronym:        | 5G-PICTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Document Number:        | D3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Document Title:         | Initial report on Data Plane Programmability and in-<br>frastructure components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Version:                | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Delivery Date:          | March 31 <sup>st</sup> 2018 ( <u>April 4<sup>th</sup> 2018</u> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Responsible:            | Consorzio Nazionale Interuniversitario per le Telecomunicazioni (CNIT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Editor(s):              | Salvatore Pontarelli (CNIT),<br>Stefan Zimmermann(ADVA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Authors:                | Jens Bartelt (AIR), August Betzler (i2CAT),<br>Giuseppe Bianchi (CNIT), Steinar Bjørnstad (TP),<br>Marco Bonola (CNIT), Daniel Camps (i2CAT), Chia-<br>Yu Chang (EUR), Jay-Kant Chaudhary (TUD), Mar-<br>cus Ehrig (IHP), Paris Flegkas (UTH), Eduard Gar-<br>cía-Villegas (i2CAT/UPC), Jesús Gutiérrez (IHP),<br>Jong Hun Han (UNIVBRIS-HPN), Joan J. Aleixendri<br>(i2CAT), Matty Kadosh (MLNX), Vaia Kalokidou<br>(UNIVBRIS-CSN), Nikos Makris (UTH), Nebojsa<br>Maletic (IHP), Peter Legg (BWT), Salvatore Pon-<br>tarelli (CNIT), Marco Spaziani (CNIT), Anna Tza-<br>nakaki (UNIVBRIS-HPN), Raimena Veisllari (TP),<br>Stefan Zimmermann(ADVA) |

| Keywords:               | Dataplane programmability, programmable network platform, optical technologies, wireless technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Status:                 | Final                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dissemination Level     | Public                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Project URL:            | http://www.5g-picture-project.eu/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# **Revision History**

| Rev. N | Description                                                   | Author                           | Date       |

|--------|---------------------------------------------------------------|----------------------------------|------------|

| 0.1    | Initial Draft                                                 | Salvatore Pontarelli<br>(CNIT)   | 07/12/2017 |

| 0.2    | First contributions integrated                                | Salvatore Pontarelli<br>(CNIT)   | 26/02/2018 |

| 0.3    | Added IHP-BWT-EUR contribution                                | Salvatore Pontarelli<br>(CNIT)   | 01/03/2018 |

| 0.4    | Added IHP contribution on MIMO                                | Jesús Gutiérrez (IHP)            | 13/03/2018 |

| 0.5    | First content check                                           | Jesús Gutiérrez (IHP)            | 14/03/2018 |

| 0.6    | Added UNIVBRIS-HPN contribution on<br>Optical Programmability | Jong Hun Han<br>(UNIVBIS-HPN)    | 15/03/2018 |

| 0.7    | First internal review                                         | Stefan Zimmermann<br>(ADVA)      | 15/03/2018 |

| 0.8    | Incorporated reviewers comments                               | Salvatore Pontarelli<br>(CNIT)   | 26/03/2018 |

| 0.9    | Incorporated additional authors                               | Salvatore Pontarelli<br>(CNIT)   | 28/03/2018 |

| 0.95   | Final technical review                                        | Anna Tzanakaki<br>(UNIVBRIS-HPN) | 03/04/2018 |

| 1.0    | Final review and submission                                   | Jesús Gutiérrez ( <b>IHP</b> )   | 04/04/2018 |

# **Table of Contents**

| LIST OF FIGURES                                         |

|---------------------------------------------------------|

| LIST OF TABLES9                                         |

| EXECUTIVE SUMMARY 10                                    |

| INTRODUCTION                                            |

| Organisation of the document11                          |

| 1 STATE OF THE ART                                      |

| 1.1 Data-plane programmability                          |

| 1.1.1 SDN/OpenFlow: limitations and extensions13        |

| 1.1.2Fully programmable data plane switches13           |

| 1.2 Optical Network Programmability15                   |

| 1.3 C-RAN programmability15                             |

| 2 DESCRIPTION OF SELECTED PLATFORMS 19                  |

| 2.1 VC709 Platform                                      |

| 2.2 NetFPGA-SUME                                        |

| 2.3 Mellanox Spectrum™ Ethernet Switch21                |

| 2.4 Xilinx Zynq UltraScale+ MPSoC ZCU102 (OAI target)21 |

| 2.5 Typhoon Platform                                    |

| 2.6 ProVMe24                                            |

| 2.7 Gateworks Ventana25                                 |

| 2.8 digiBackBoard                                       |

| 2.8.1 digiBackBoard as a wireless communications node26 |

| 2.8.2 digiBackBoard as an interface across technologies |

| 2.9 Xilinx VCU-110                                      |

| 2.9.1 Evaluation platform                               |

| 2.9.2 Faster technology SFP+ interface board FM-S18     |

| 2.9.3 Block diagram                                     |

| 2.10 IAF 5G Development Platform (F-PU 5G)              |

| 3 FUNCTIONAL DEFINITION OF PROGRAMMABLE PLATFORMS       |

| 3.1<br>FH/BH |        | agent and controller development for control- and data-plane in Optical transport in support of join | t    |

|--------------|--------|------------------------------------------------------------------------------------------------------|------|

| 3.2          | Arch   | itectural definition of programmable C-RAN                                                           | 33   |

| 3.3          | Ope    | n Packet Processor (OPP)                                                                             | 34   |

| 3.3.         | •      | Per-flow stateful model                                                                              |      |

| 3.3.         | 2      | Aggregation tasks and lazy evaluation functions                                                      |      |

| 3.3.         | 3      | Calendar                                                                                             | 37   |

| 3.3.         | 4      | Packet Manipulator Processor                                                                         | 38   |

| 3.4          | ΟΑΙ    | platform for SDN-based programmable network functions                                                | 40   |

| 3.5          | Port   | ing of OAI on the Zynq platform                                                                      | 42   |

| 3.6          | Poin   | t-to-Multipoint (P2MP) MAC processor                                                                 | 43   |

| 3.6.         | 1      | Objectives                                                                                           |      |

| 3.6.         | 2      | Installation and link establishment                                                                  |      |

| 3.6.         | 3      | Mesh network architectures/topologies                                                                |      |

| 3.6.         |        | Medium access                                                                                        | 45   |

| 3            | .6.4.1 |                                                                                                      |      |

| -            | .6.4.2 |                                                                                                      |      |

| 3.6.         | 5      | Functionalities of the MAC layer                                                                     | 45   |

| 3.7<br>4 H   |        | CONF server and Yang models for Time Sensitive Networks (TSN)                                        |      |

| 4.1          | APIs   |                                                                                                      | 48   |

| 4.1.         | 1      | APIs for the BWT Typhoon platform                                                                    | 48   |

| 4.1.         | 2      | APIs for the GateWorks Ventana platform.                                                             | 48   |

| 4.1.         | 3      | Ethernet-based API for Read/write of FPGA registers                                                  | 50   |

| 4.2          | OAI    | or Interface for Physical Network Functions                                                          | 50   |

| 4.3          | Pros   | ramming languages for data plane programmability                                                     | 51   |

| 4.3.         |        | OpenCL development of network functionalities                                                        |      |

| 4.3.         |        | Development of P4 compiler for Spectrum device                                                       |      |

|              | .3.2.1 |                                                                                                      |      |

| 5 H          | IARI   | DWARE TECHNOLOGIES                                                                                   | . 54 |

| 5.1          | Pass   | ive optical technologies                                                                             | 54   |

| 5.2          |        | tic optical technologies                                                                             |      |

| 5.2          |        |                                                                                                      |      |

| 5.3          |        | e sensitive Ethernet                                                                                 |      |

| 5.3.         |        | Deterministic delay mechanisms for Ethernet                                                          |      |

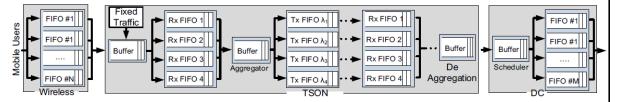

| 5.3.         | 2      | Bounded delay aggregation and fixed delay forwarding                                                 | 57   |

| 5.4          | RF p   | rocessing and modelling                                                                              | 57   |

| 5.4.         | 1      | Ray-tracing Tool                                                                                     | 58   |

| 5            | .4.1.1 | Sub-6 GHz LTE Massive MIMO coverage cell                                                             | 58   |

| 5            | .4.1.2 |                                                                                                      |      |

|              |        |                                                                                                      |      |

### 5G-PICTURE Deliverable

| 5.5.1       SDN enabled routing and forwarding between RU and BBU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.5 RF/E | 3B processing                                                    | 60    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------|-------|

| 5.5.3       C-RAN functional split as programmable network function       61         5.5.4       DSP and Layer-1 Functions Integrated into Radio Units       63         5.5.4.1       AADU Architecture       63         5.5.4.2       AADU Functions and Processors       64         5.5.4.3       AADU Functional Split       65         5.5.4.4       Interconnect architecture       66         5.6       MIMO at mmWave       67         5.6.1       LoS MIMO at mmWave frequencies       69         5.6.2       RF front-ends for MIMO at mmWave       70         5.7       Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)       71         5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75 | 5.5.1    | SDN enabled routing and forwarding between RU and BBU            | 60    |

| 5.5.4       DSP and Layer-1 Functions Integrated into Radio Units       63         5.5.4.1       AADU Architecture       63         5.5.4.2       AADU Functions and Processors       64         5.5.4.3       AADU Functional Split       65         5.5.4.4       Interconnect architecture       66         5.6       MIMO at mmWave       67         5.6.1       LoS MIMO at mmWave frequencies       69         5.6.2       RF front-ends for MIMO at mmWave       70         5.7       Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)       71         5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                      | 5.5.2    | In-Band E-CPRI for enhanced synchronization                      | 61    |

| 5.5.4.1       AADU Architecture       63         5.5.4.2       AADU Functions and Processors       64         5.5.4.3       AADU Functional Split       65         5.5.4.4       Interconnect architecture       66         5.6       MIMO at mmWave       67         5.6.1       LoS MIMO at mmWave frequencies       69         5.6.2       RF front-ends for MIMO at mmWave       70         5.7       Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)       71         5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                                                                                                         | 5.5.3    | C-RAN functional split as programmable network function          | 61    |

| 5.5.4.2       AADU Functions and Processors       64         5.5.4.3       AADU Functional Split       65         5.5.4.4       Interconnect architecture       66         5.6       MIMO at mmWave       67         5.6.1       LoS MIMO at mmWave frequencies       69         5.6.2       RF front-ends for MIMO at mmWave       70         5.7       Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)       71         5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                                                                                                                                                          | 5.5.4    | DSP and Layer-1 Functions Integrated into Radio Units            | 63    |

| 5.5.4.3       AADU Functional Split       65         5.5.4.4       Interconnect architecture       66         5.6       MIMO at mmWave       67         5.6.1       LoS MIMO at mmWave frequencies       69         5.6.2       RF front-ends for MIMO at mmWave       70         5.7       Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)       71         5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                                                                                                                                                                                                                       | 5.5.4.1  | AADU Architecture                                                | 63    |

| 5.5.4.4       Interconnect architecture       66         5.6       MIMO at mmWave       67         5.6.1       LoS MIMO at mmWave frequencies       69         5.6.2       RF front-ends for MIMO at mmWave       70         5.7       Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)       71         5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                                                                                                                                                                                                                                                                            | 5.5.4.2  | AADU Functions and Processors                                    | 64    |

| 5.6       MIMO at mmWave       67         5.6.1       LoS MIMO at mmWave frequencies       69         5.6.2       RF front-ends for MIMO at mmWave       70         5.7       Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)       71         5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                                                                                                                                                                                                                                                                                                                                     | 5.5.4.3  | AADU Functional Split                                            | 65    |

| 5.6.1LoS MIMO at mmWave frequencies695.6.2RF front-ends for MIMO at mmWave705.7Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)715.7.1Initial design for optical edge nodes715.7.2Traffic adaptation at lower layers725.7.3Synchronization726SUMMARY AND CONCLUSIONS747REFERENCES75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.5.4.4  | Interconnect architecture                                        |       |

| 5.6.1LoS MIMO at mmWave frequencies695.6.2RF front-ends for MIMO at mmWave705.7Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)715.7.1Initial design for optical edge nodes715.7.2Traffic adaptation at lower layers725.7.3Synchronization726SUMMARY AND CONCLUSIONS747REFERENCES75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                                                  |       |

| 5.6.2RF front-ends for MIMO at mmWave705.7Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)715.7.1Initial design for optical edge nodes715.7.2Traffic adaptation at lower layers725.7.3Synchronization726SUMMARY AND CONCLUSIONS747REFERENCES75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.6 MIN  | 10 at mmWave                                                     | 67    |

| 5.6.2RF front-ends for MIMO at mmWave705.7Interfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs)715.7.1Initial design for optical edge nodes715.7.2Traffic adaptation at lower layers725.7.3Synchronization726SUMMARY AND CONCLUSIONS747REFERENCES75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.6.1    | LoS MIMO at mmWave frequencies                                   | 69    |

| 5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.6.2    |                                                                  |       |

| 5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                                                  |       |

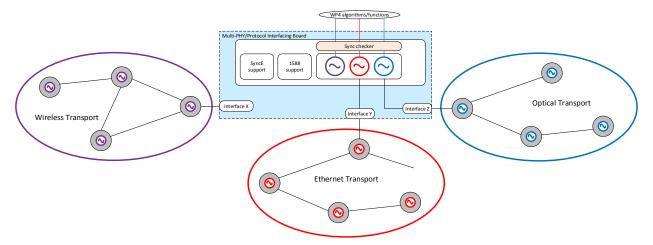

| 5.7.1       Initial design for optical edge nodes       71         5.7.2       Traffic adaptation at lower layers       72         5.7.3       Synchronization       72         6       SUMMARY AND CONCLUSIONS       74         7       REFERENCES       75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.7 Inte | rfaces - Multi-Protocol / Multi-PHY interfacing functions (MPIs) | 71    |

| 5.7.3       Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                                                  |       |

| 5.7.3       Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.7.2    | Traffic adaptation at lower layers                               | 72    |

| 7 REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.7.3    |                                                                  |       |

| 7 REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                                                  |       |

| 7 REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <        |                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6 SUM    | MARY AND CONCLUSIONS                                             |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7 RFFF   | RENCES                                                           | 75    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | , NLIL   |                                                                  | / / / |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                  |       |

| 8 ACKUNYMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8 ACRO   | DNYMS                                                            |       |

| 8 ACKONYMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8 ACRO   | )NYMS                                                            |       |

# **List of Figures**

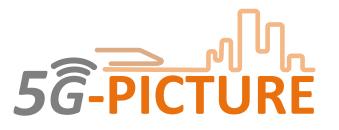

| Figure 1: FDD LTE timing                                                                                                                                                                           | 16 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

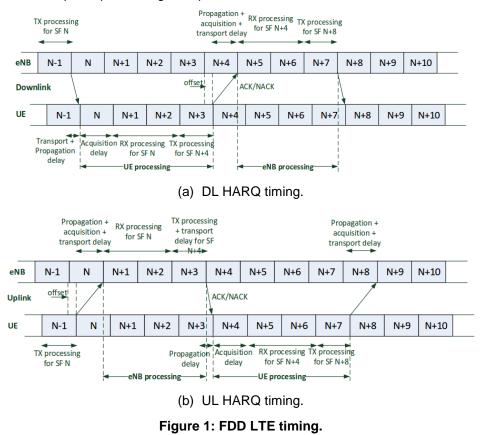

| Figure 2: User data plane forwarding path in disaggregated RAN                                                                                                                                     | 17 |

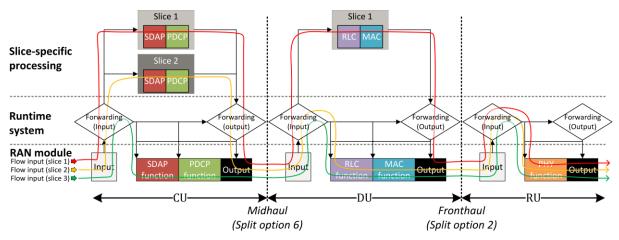

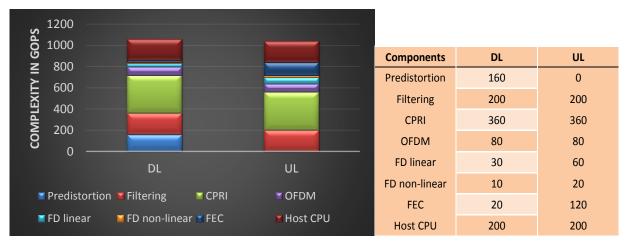

| Figure 3: An exemplary plot of computational complexity in GOPS verses downlink throughput for difference user certain time <i>t</i> .                                                             |    |

| Figure 4: An exemplary plot showing computational complexity in GOPS in UL and DL for different compon of macro cell site.                                                                         |    |

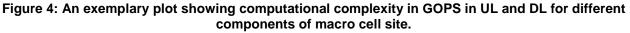

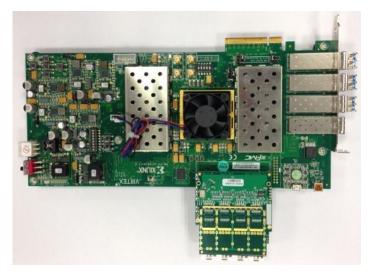

| Figure 5: VC709 with 4x 10G SFP+ FMC card                                                                                                                                                          | 19 |

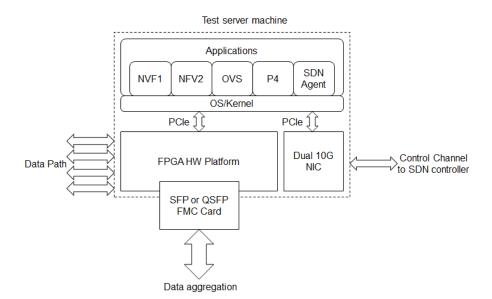

| Figure 6: A block diagram of server test machine with the FPGA platform and the FMC card                                                                                                           | 20 |

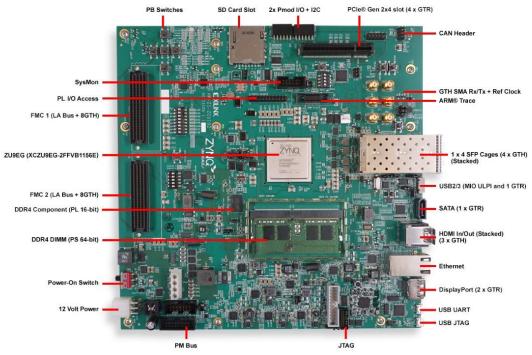

| Figure 7: Xilinx Zynq ZCU102 interfaces                                                                                                                                                            | 22 |

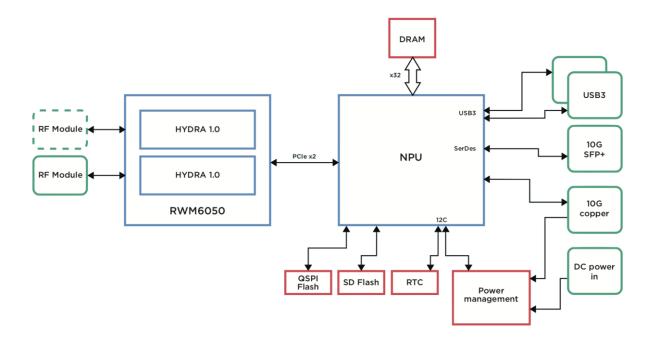

| Figure 8: BWT Typhoon block diagram                                                                                                                                                                | 24 |

| Figure 9: ADVA FSP 150 ProVMe series                                                                                                                                                               | 24 |

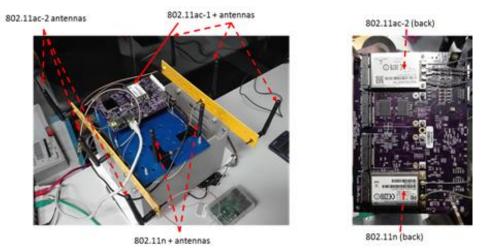

| Figure 10: Gateworks Ventana platform equipped with 3 wireless NICs and omnidirectional antennas                                                                                                   | 25 |

| Figure 11: IHP's digiBackBoard                                                                                                                                                                     | 26 |

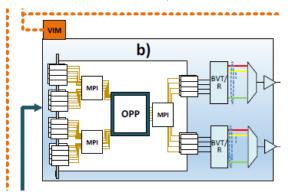

| Figure 12: Possible use of the MPI to interconnect different programmable blocks.                                                                                                                  | 27 |

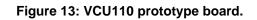

| Figure 13: VCU110 prototype board                                                                                                                                                                  | 28 |

| Figure 14: FM-S18                                                                                                                                                                                  | 28 |

| Figure 15: 100G IP Core evaluation platform.                                                                                                                                                       | 29 |

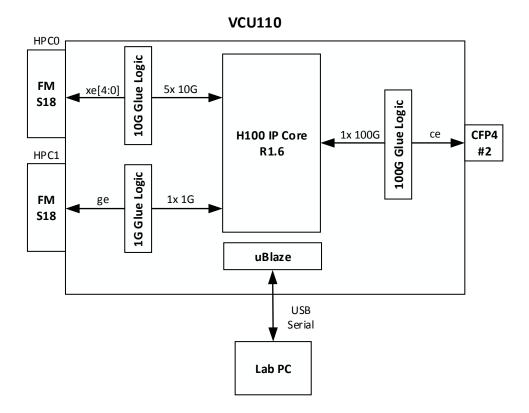

| Figure 16: IAF 5G Development Platform.                                                                                                                                                            | 30 |

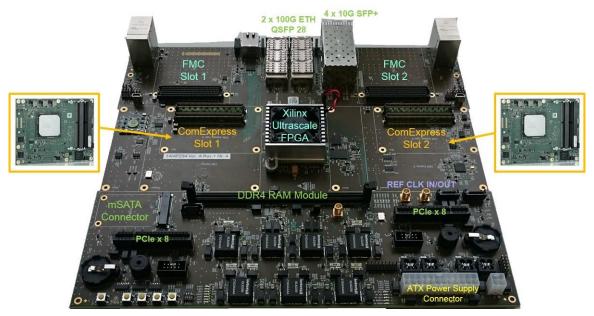

| Figure 17: F-PU 5G block diagram                                                                                                                                                                   | 31 |

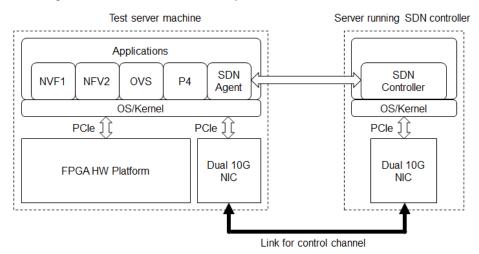

| Figure 18: Configuration for the development of an agent and controller for SDN.                                                                                                                   | 32 |

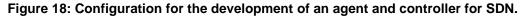

| Figure 19: Network connection for SDN enabled RU and BBU.                                                                                                                                          | 33 |

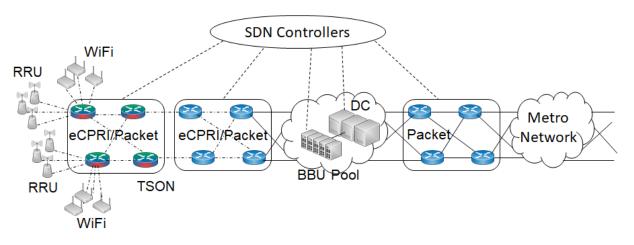

| Figure 20: Architecture of OPP                                                                                                                                                                     | 34 |

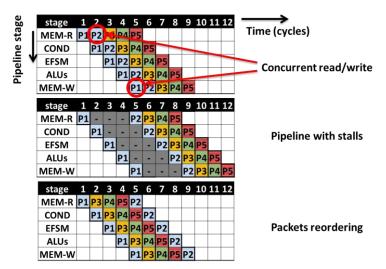

| Figure 21: Stateful element scheduling options. P1 and P2 belong to the same flow therefore they use same flow context. P3, P4 and P5 belong to different flows and can concurrently access memory |    |

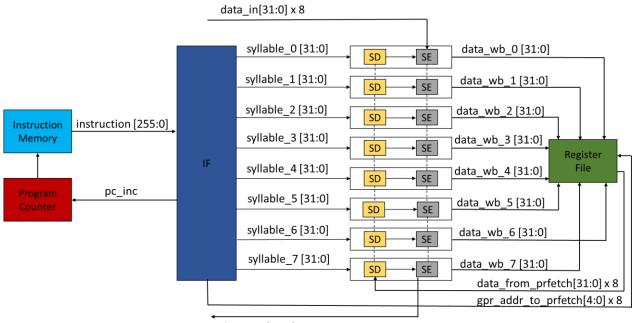

| Figure 22: PMP top architecture                                                                                                                                                                    | 38 |

| Figure 23: PMP Single lane structure                                                                                                                                                               | 39 |

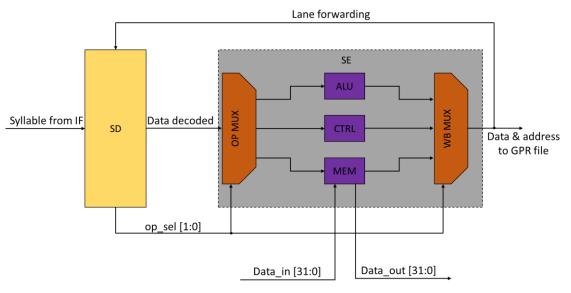

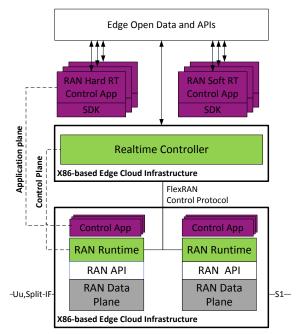

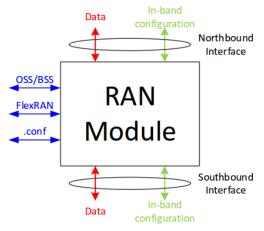

| Figure 24: OpenAirInterface and FlexRAN platforms to support SD-RAN                                                                                                                                | 40 |

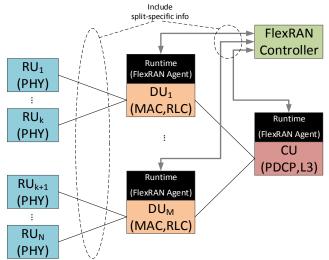

| Figure 25: Multi-agent model and FlexRAN controller in a disaggregated RAN                                                                                                                         | 42 |

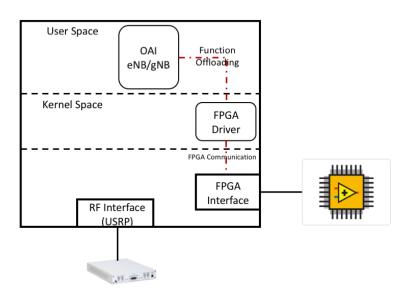

| Figure 26: FPGA offloading process for the OAI RAN.                                                                                                                                                | 43 |

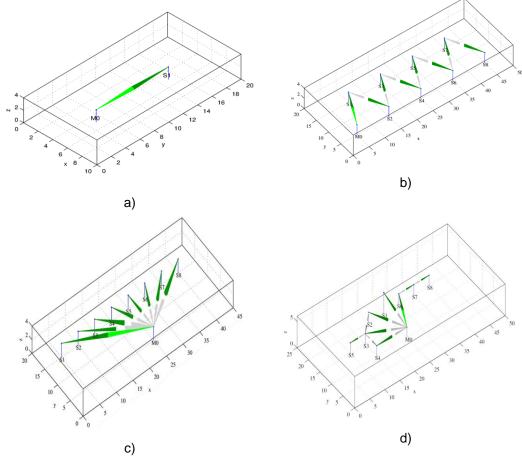

| Figure 27: a) single hop point-to-point, b) daisy chain, c) single hop point-to-multipoint, d) complex mesh.                                                                                       | 44 |

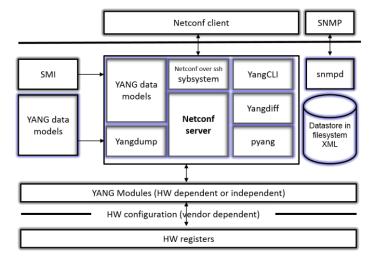

| Figure 28: The Yuma123 framework                                                                                                                                                                   | 46 |

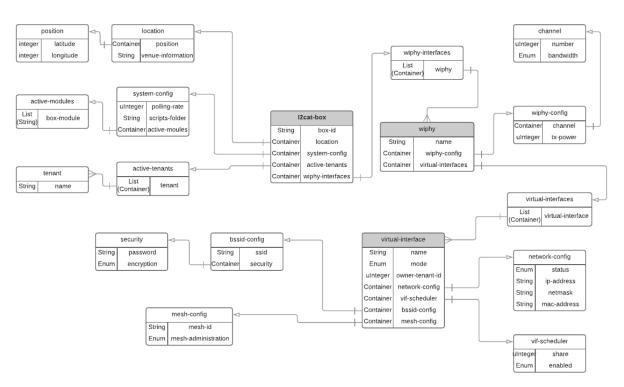

| Figure 29: Yang model of the I2cat-box.                                                                                                                                                            | 49 |

| Figure 30: the Ethernet frame for Read/write of FPGA registers.                                                                                                                                    | 50 |

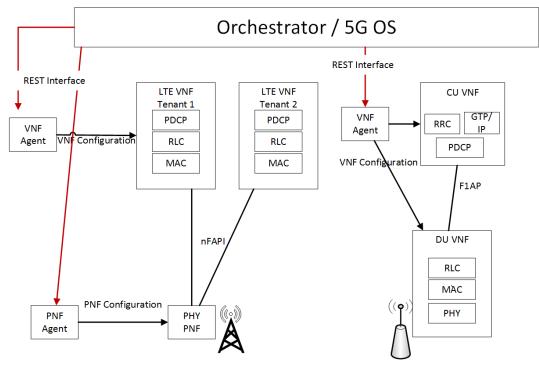

| Figure 31: High level Agent description for handling OAI PNFs and VNFs                                                                                                                             | 51 |

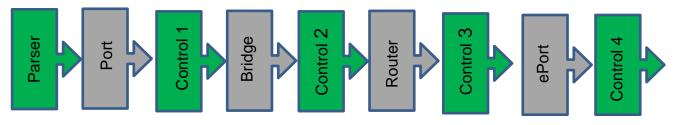

| Figure 32. Mellanox's P4 target architecture.                                                                                                                                                      | 52 |

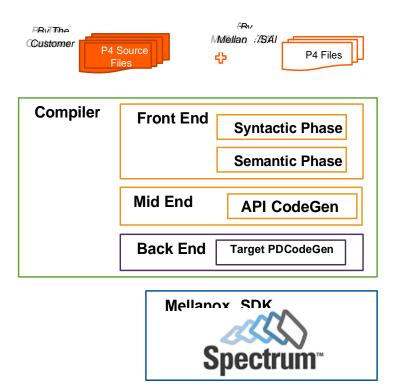

| Figure 33. P4 compiler architecture                                                                                                                                                                | 53 |

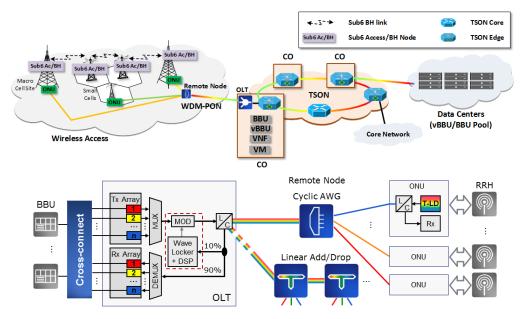

| Figure 34: ADVA's WDM-PON in the 5G-XHaul network                                                                                                                                                  | 54 |

|                                                                                                                                                                                                    |    |

### 5G-PICTURE Deliverable

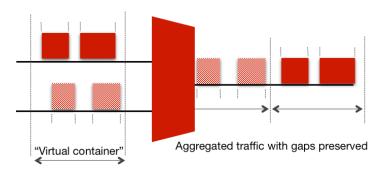

| Figure 35: Aggregation of multiple deterministic packets streams into virtual containers while preserving packet gaps                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

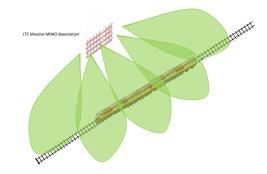

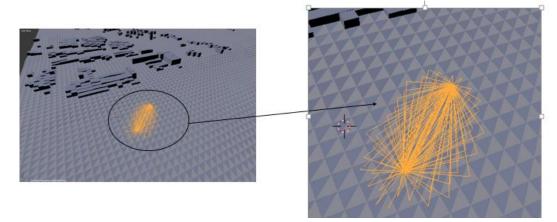

| Figure 36. Vertical Rail – Sub-6 GHz LTE Massive MIMO cell                                                                                                |

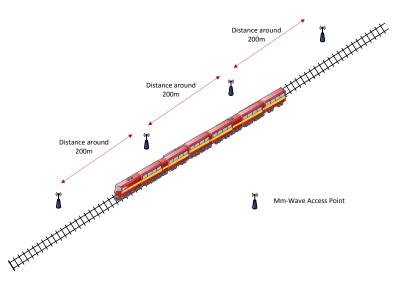

| Figure 37. Vertical Rail – mmWave APs along trackside                                                                                                     |

| Figure 38. Bristol Temple Meads route (1.4 km)                                                                                                            |

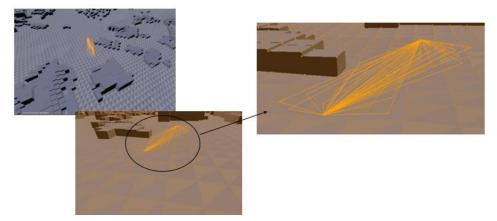

| Figure 39. Bristol Temple Meads - Rays for a specific point                                                                                               |

| Figure 40. London Paddington route (3.5 km)                                                                                                               |

| Figure 41. London Paddington – Rays for a specific point                                                                                                  |

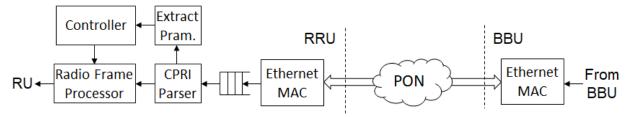

| Figure 42. In-Band eCPRI protocol processing unit                                                                                                         |

| Figure 43: Generic Interface Ports for OAI Entities                                                                                                       |

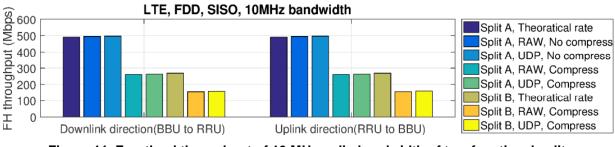

| Figure 44: Fronthaul throughput of 10 MHz radio bandwidth of two functional split                                                                         |

| Figure 45: RU prototype                                                                                                                                   |

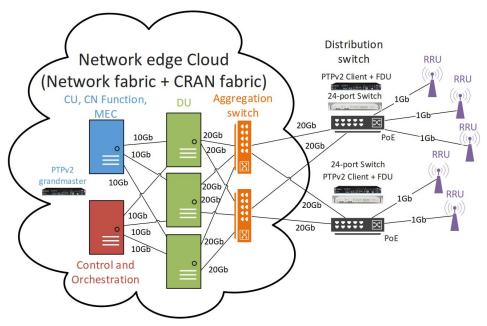

| Figure 46: Logical C-RAN deployment example                                                                                                               |

| Figure 47: AADU overall architecture                                                                                                                      |

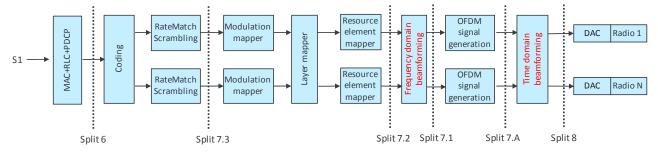

| Figure 48: Physical layer processing chain                                                                                                                |

| Figure 49: AADU hardware architecture                                                                                                                     |

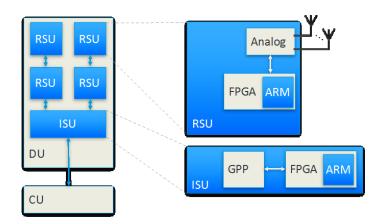

| Figure 50: AADU functional split options                                                                                                                  |

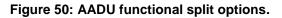

| Figure 51: AADU interconnect options                                                                                                                      |

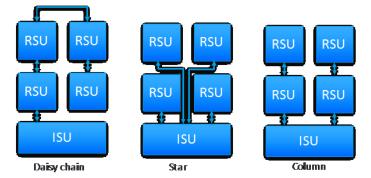

| Figure 52: RF analogue beamforming mmWave MIMO system supporting single stream transmission 67                                                            |

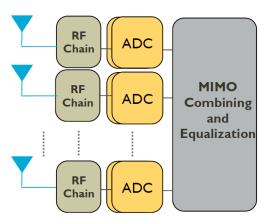

| Figure 53: Conventional MIMO where all the signal processing is done in digital domain                                                                    |

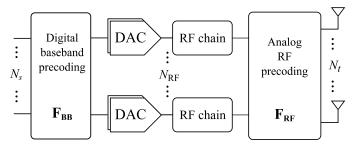

| Figure 54: Hybrid precoding transmitter architecture                                                                                                      |

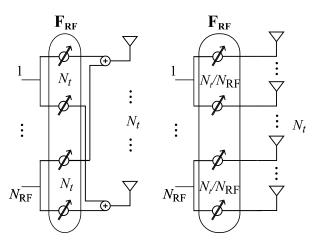

| Figure 55: RF Analogue beamforming structures: fully-interconnected structure (left), partially-interconnected structure (right)                          |

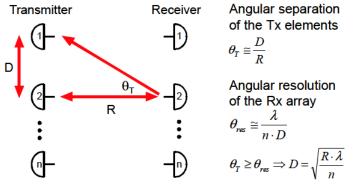

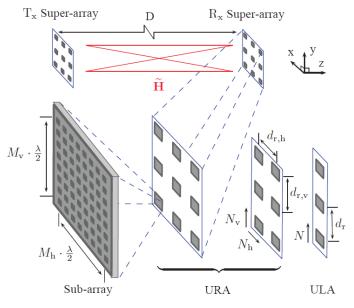

| Figure 56: LOS MIMO system [58] 69                                                                                                                        |

| Figure 57: LOS MIMO system with super-arrays [59] 69                                                                                                      |

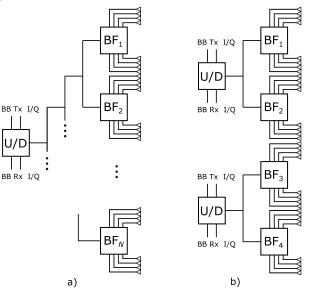

| Figure 58: Examples of different mmWave beamforming architectures: a) massive mmWave array, b) hybrid beamforming mmWave MIMO architecture with subarrays |

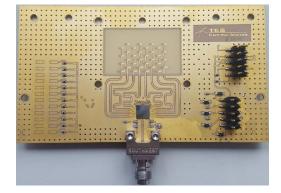

| Figure 59: 60 GHz RF front-ends: RF board with beamforming to be used with off-the-shelf up/down converter (left) and complete RF front-end board (right) |

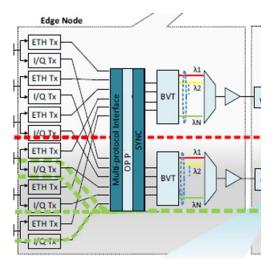

| Figure 60: Edge node equipped with HW programmability features72                                                                                          |

| Figure 61: Example of streams coming from the wireless access domain to the optical transport domain 72                                                   |

| Figure 62: Multi-PHY/Multi-Protocol Interfacing solution enabling synchronization across technology domains.                                              |

|                                                                                                                                                           |

# **List of Tables**

| Table 1: Key characteristics of the Xilinx Zynq ZCU102. | 22 |

|---------------------------------------------------------|----|

| Table 2: FlexRAN API calls.                             | 41 |

| Table 3: Data rate for different AADU options.          | 67 |

## **Executive Summary**

This document corresponds to deliverable D3.1, "Initial report on Data Plane Programmability and infrastructure components" of the H2020 5G-PICTURE project. The deliverable provides the description of the platforms for data plane programmability and the initial specification of the interfaces, programming models, and hardware abstractions that will be developed during the course of the project.

Several solutions for data plane programmability, dealing with the design and implementation of programming platforms for both fronthaul/signal processing and backhaul/packet processing are presented together with the relevant exposed methods to abstract the underlying platforms. Finally, the deliverable reports the study on infrastructure components and multi-protocol/multi-PHY interfacing technologies.

A more precise and definitive detailed architectural description of the programmable platforms will be provided in deliverable D3.2, with due date November 2018.

### Introduction

Network nodes (being wired switches, radio stations, or even end terminals) have been traditionally developed for extremely specific purposes: support a given and possibly small set of **communication or forwarding needs**. Indeed, innovation was (and of course still is) driven by lengthy standardization processes, devised to specify the behaviour and the inter-operation of the nodes and to formalize such specification into one or more protocols, independently implemented once for all by device vendors in closed products. This historical trend allowed the widespread diffusion of several network technologies providing a constant improvement of the network nodes performance.

Unfortunately, networks today are extremely complex and diversified: the original Internet nodes, historically limited to switches and routers, have been massively complemented with a variety of heterogeneous middleboxes, such as network address translators, tunnelling entities, load balancers, firewalls, intrusion detection systems, traffic monitoring probes, etc. The networks today must be made able to promptly accommodate (in very different environments) very diverse end points, from handheld devices to sensors and actuators integrated into physical objects (the so-called "Internet of Things"), and are called to sustain a dramatic evolution not only in terms of scale ("big data"), but also in terms of complexity and diversity in their traffic generation patterns and relevant requirements (human end points, machine-to-machine relations, content retrieval from caching and replica servers, flash crowd events, etc.).

This complex scenario makes much more difficult to maintain the above mentioned development model of network nodes in which they were designed to efficiently perform an extremely specific task and to support a well-defined set of protocols. Instead, today it is more and more important to have flexible and reconfigurable network nodes that are able to: i) support different sets of functionalities depending on the specific network location in which they are deployed; ii) dynamically change the supported set of functionalities depending on the network condition and/or the type of traffic/service to manage and iii) be easily upgradable if different service/protocols arise. On the other hand, this flexibility cannot be traded off against network performances.

In this scenario programmable network platforms are the enabling factor that allows developing complex network functionalities without compromising the performance levels achievable with fixed purpose network devices. These platforms should provide several common aspects in the different network domains (dataplane, optical, and radio access). The programmable network platforms must provide clear programming models that will allow development of network functions (NFs), decoupling the definition of the function from the specific platform-dependent implementation. Possible programming models are for example the Domain Specific Languages (DSLs) such as P4 language for programmable dataplanes or the OpenCL language for the definition of digital signal processing (DSP) radio functions. Moreover, the control/data plane separation enabled by the use of SDN technologies that is dominating the wired network scenario can be extremely useful also in the radio and optical network domains. Finally, a set of hardware abstractions and/or interfaces must be developed to provide to the upper layers of the network management a sort of API to easily manage the configuration of the programmable platforms.

This deliverable discusses the initial specification of the interfaces, programming models, and hardware abstractions of the programmable network platforms that will be developed in the 5G-PICTURE project.

#### Organisation of the document

This deliverable is structured as follows: Section 1 provides a state-of-the-art review programmability of different network technologies. This includes dataplane, optical network, and radio access network. In section 2, the document presents the various target hardware platforms selected by the 5G-PICTURE partners as foundations for their programmable network platforms. Some of the hardware platforms are result of development work performed by some specific partners. The functionalities of these platforms will be enhanced and/or further exploited for improving programmability capabilities. Some of the other hardware platforms are off-theshelf platform acquired by the partners. In the latter case, the platform choices are not only based on partnerspecific programmability requirements, but also on easy integration of the work done by different partners. Section 3 presents the initial functional definitions of the programmable platforms that are under development in the current phase of the project and will be finalized in deliverable D3.2. The platform programmability requires a set of methodologies allowing common abstractions of the underlying hardware. Those methodologies, or simply called hardware abstractions, are presented in section 4. Section 5 illustrates the different

hardware technologies developed in 5G-PICTURE that provide basic building blocks of the 5G network architecture, comprising novel passive and elastic optical as well as RF and baseband (BB) processing technologies. Finally, section 6 contains the summary and conclusions.

### 1 State of The Art

This section summarises the State-of-The-Art (SoTA) of the programmability features of different network elements composing the 5G scenario. In particular, it describes the programmability of data plane, optical network, and C-RAN.

#### 1.1 Data-plane programmability

5G networks must efficiently and flexibly support an ever growing variety of heterogeneous middlebox-type functions such as network address translation, tunneling, load balancing, traffic engineering, monitoring, intrusion detection, etc. In the last years, the community has attempted to address the programmability of such network functions with two complementary approaches: Software-Defined Networking (SDN) and Network Function Virtualization (NFV).

However, these approaches have so far remained disjoint. SDN has focused on the clean separation of control and data plane via open interfaces. It has exploited re-configurability of high performance switching hardware only to a very small extent (i.e. due to the limited flexibility of OpenFlow [1] as southbound interface). Conversely, NFV has fostered full programmability of network functions, but mainly via SW on commodity platforms. Hence it is subject to performance limitations, and in general not relying on open programming interfaces. In this section, we first describe the SDN/OpenFlow limitations, and then we discuss the most up-to-date research and industrial initiatives that aim to supersede these limitations.

#### 1.1.1 SDN/OpenFlow: limitations and extensions

Early SDN approaches (and still most of today's real world deployments) rely on the relatively poorly flexible OpenFlow abstraction as southbound (i.e. node-level, using RFC 7426's terminology) programming interface. OpenFlow is perfectly suited to configure forwarding behaviours executed at wire speed in the switches, expressed as switch/router flow tables, but *shows severe limitations when it comes to deploy more complex (e.g. stateful) flow processing and filtering functions*. For this reason, most of today's network programming frameworks circumvent OpenFlow's limitations by promoting a "two-tiered" [2] programming model: any stateful processing intelligence of the network applications is delegated to the network controller, whereas OpenFlow switches are limited to install and enforce stateless packet forwarding rules delivered by the remote controller. This delegation of intelligence to the centralized controller thus causes performance, latency, and signalling overhead, which hinders the deployment of truly scalable software-implemented control plane *tasks at wire speed*, i.e. while remaining on the fast path.

This problem is of course not new, and also well-known by the Open Networking Foundation (ONF), the body which standardises OpenFlow since 2011. Indeed, in the course of the OpenFlow standardisation process, we have witnessed a hectic evolution of the standard, but backward compatibility reasons and pragmatism have so far prevented OpenFlow from incorporating the flexibility necessary for implementing advanced packet processing tasks. As a matter of fact, and up to the latest specification version 1.5 [3], several OpenFlow extensions have been devised to fix punctual shortcomings and accommodate specific needs. Such evolution has led to the incorporation of extremely specific stateful primitives into the OpenFlow standard (such as meters for rate control, group ports for fast failover support or dynamic selection of one among many action buckets at each time - e.g. for load balancing -, synchronized tables for supporting learning-type functionalities, etc. see details in [3]). Despite such many tailored OpenFlow extensions, we are still very far from being able to deploy typical Middlebox appliance features in an OpenFlow switch. At the same time, another limitation of the OpenFlow approach is emerging. It is related to the way the header fields are defined in the OpenFlow standard. In fact, the standard explicitly defines the specific packet fields that are used as inputs for the OpenFlow match/action stages. Therefore, it is not possible to use a custom defined header for the matching stages. This limitation has been faced until now by defining a new set of fields in each revision of the standard. The first OpenFlow version had only 12 fields, while the OF1.5 revision defines up to 42 fields [3]. Since this approach was not sustainable, the proposal of a complete protocol independent packet processing has emerged [4].

#### 1.1.2 Fully programmable data plane switches

As already mentioned, even if NFV in principle addresses full programmability of network functions, it comes with two fundamental caveats. First, approaches proposed so far do not provide an "open" programming model for the data plane operation of the network function itself. Second, fast-path (wire speed) processing in SW for multi gigabit/s links, even if in principle attainable with massive multi-core parallelization and Network Interface Card (NIC)-level accelerations, e.g. Data Plane Development Kit (DPDK), remains extremely demanding, es-

### 5G-PICTURE Deliverable

pecially when the design goal is to retain independence from the underlying platform. The point is that *involv-ing a CPU in packet-by-packet processing comes with an overly severe overhead* (with multiple micro-instructions frequently necessary to perform a packet-level operation that in HW could be even implemented within just a clock cycle). It is hardly compatible with the very tight requirements of a wire-speed/fast-path processing task (a 64 bytes packet takes only about 5 ns on a 100 Gb/s speed). And, to make things worse, software solutions cannot take advantage of dedicated HW components, such as Ternary Content-Addressable Memories (TCAMs), which can trivially solve problems like wildcard matching in O(1) complexity. As of now, it does not yet exists an equivalent O(1) complexity software implementation counterpart.

For these reasons, in the last couple of years, a new research trend has started to challenge improved programmability of the data plane via domain-specific packet processing HW platforms or chipsets, which still attempt to expose very flexible and general programming interfaces and languages (somewhat comparable to CPU-based programming), but are specifically designed for packet-level processing tasks.

Probably *the most popular initiative in this fresh field is P4* [4]. The P4 initiative started from the observation that while in the past network switches had a fixed and well-known behaviour, today a new generation of fully reprogrammable high speed HW switch architectures is emerging. Representative example architectures include the reconfigurable match tables introduced in [35], the Intel FlexPipe technology [5] and, at least to some extent, the way more flexible header matching promoted by the Huawei Protocol Oblivious Forwarding (POF) initiative [6]. The P4 programming language [4] thus emerged as an attempt to **programmatically describe the packet processing pipeline** [35] via "packet programs" written in a high level language that can be compiled for different HW targets. Still, despite the current P4 hype and the significant attention that P4 has received by the networking community, it is at least fair to say that P4 is not yet "the" solution to "all possible" data-plane programming needs. We specifically see at least three major open issues, which motivate (and give the basis of) our planned work within the 5G-PICTURE project.

First, P4 is of course NOT a programmable switch architecture, but it is (and remains) a programming language which, as such, requires some underlying HW architectures (chipsets) capable of "running" P4 packet programs. Surprisingly, while P4 "as a language" has been dissected into full details, very little research has been disclosed so far on the platforms devised to support it. In the last year several industrial initiatives started to provide P4 compatible hardware platforms: the Barefoot Tofino<sup>™</sup> programmable switch series has been presented few months ago<sup>1</sup>, the Netronome Smart NIC is able to use P4 as a programming language<sup>2</sup>, and also a Field Programmable Gate Array (FPGA) based board from Netcope<sup>3</sup> has recently appeared in the market. The analysis and the design of novel hardware architectures able to support P4 programmability seems to be a novel and fast growing research activity with still many open questions. One of the scopes of 5G-PICTURE is thus to understand how to compile P4 programs for already existing HW platforms (HW platforms provided by the switch manufacturers involved in 5G-PICTURE), and, complementarily, (ii) how to extend current HW to support P4 packet programs. A second, and perhaps even more fundamental question, relates to thoroughly understanding if there are limitations in how P4 permits to describe some subset of wire-speed flow/packet processing tasks and, if this is the case, how to extend P4 capabilities - or identify novel approaches - to cover such gaps. It is a fact that P4 was initially devised with "only" packetlevel processing tasks in mind, i.e. processing tasks which take as input a given packet and process it (and forward it) on the basis of information associated with the packet itself (e.g. packet structure). Stateful processing was thus initially restricted to "packet-level states" (e.g. states specified while parsing an individual packet), opposed to "flow-level states", i.e. states which persist (and which are updated) across subsequent packets of the same flow. With version 1.0.2 [7], the P4 specification has made a further initial step in supporting per-flow stateful processing by introducing registers defined as stateful memories, which can be used in a more general way to keep state. However, these stateful constructs seem to be sort of a "side-patch" to P4 (opposed to a native fundamental feature) whose support is mandated to the actual target platform. Indeed, the P4 language does not natively provide means to address and fetch registries (or counters) or means to associate registries with flows without incurring in access collisions<sup>4</sup>. Rather, as explicitly stated in

<sup>&</sup>lt;sup>1</sup> <u>https://www.barefootnetworks.com/products/brief-tofino/</u>

<sup>&</sup>lt;sup>2</sup> <u>https://www.netronome.com/technology/p4/</u>

<sup>&</sup>lt;sup>3</sup> <u>https://www.netcope.com/en/products/netcopep4</u>

<sup>&</sup>lt;sup>4</sup> The technical underlying problem is how to persistently associate a register to a flow. Without any dedicated primitive or data structure providing such an association, most P4 algorithms circumvent such problem by exploiting an Hash-value generator, provided as P4 language primitive, which associates an integer value to any arbitrary bitstring (e.g. a flow name). Such an associated integer can be then

the latest language specification [8], stateful constructs such as counters and meters are represented using external objects and must be explicitly supported by the target and allocated at compilation-time through a process called "instantiation". To address such shortcomings, 5G-PICTURE is specifically focusing on innovative abstractions for describing stateful flow processing, and on the design of the underlying architectures devised to support such abstractions as will be discussed in section 3.3.

#### 1.2 Optical Network Programmability